#### **Integrated Circuits**

M. Garcia-Sciveres Lawrence Berkeley National Lab

> Physics 290E Jan. 31, 2018

# Introduction

GOAL: Encourage you to learn more about integrated circuits Exposure to some concepts and words you'll hear IC designers speak.

- Where are integrated circuits used? ASICs

- History and HEP history

- Special place of Berkeley

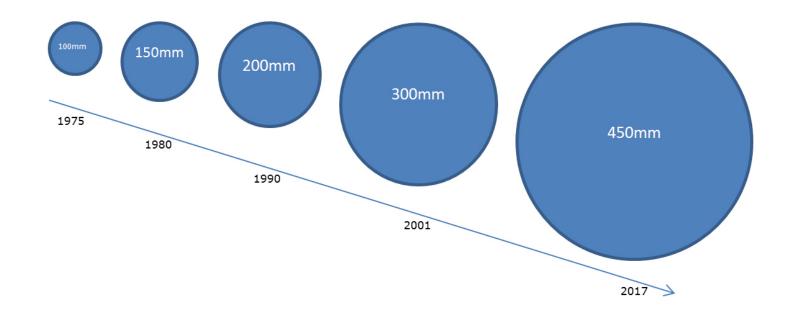

- How are ICs made?

- How are ICs designed

- Special needs of physics experiments

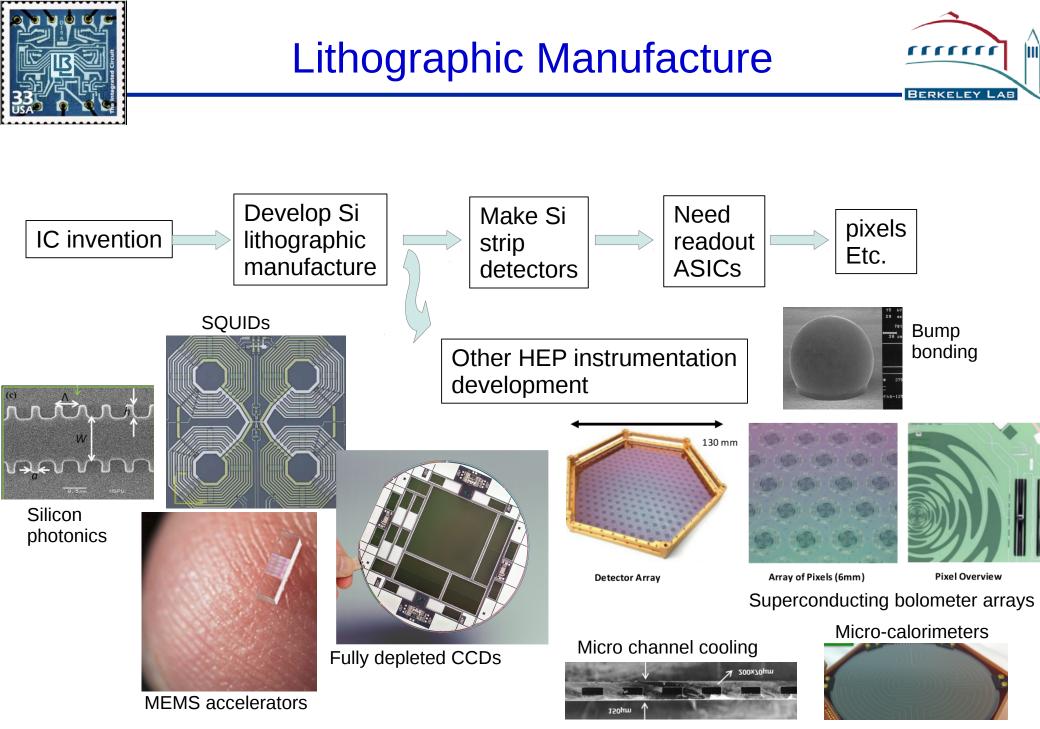

- Lithographic fabrication beyond IC's enables many experiments

• ASIC = Application Specific Integrated Circuit

verilog Design mismatch repository tho Digital om 0/0 rners 9/ nstrained transistor logic EDA

GOAL: To encourage you to take seriously learning more about integrated circuits Exposure to some concepts and words you'll use IC designers speak.

- Where are integrated circuits used? ASICs

- History and HEP history

- Special place of Berkeley

- How are ICs made?

- How are ICs designed

- Special needs of physics experiments

- Lithographic fabrication beyond IC's enables many experiments

• ASIC = Application Specific Integrated Circuit

# List of ASICs in ATLAS

| The alatin a                      |                      |                        |                                        | Occurrentities 0           |    | Calorime           | eters | ASIC               | Tee            | chnology                  | Functionality                     | Quantity & remarks          |

|-----------------------------------|----------------------|------------------------|----------------------------------------|----------------------------|----|--------------------|-------|--------------------|----------------|---------------------------|-----------------------------------|-----------------------------|

| Tracking<br>detectors             | ASIC                 | Technology             | Functionality                          | Quantity & remarks         |    | LAr<br>Calorimeter |       | HAMAC-<br>SCA      | DN             | <b>/</b> ILL              | Analogue<br>memory                | ~52000                      |

| Pixel<br>Silicon<br>Strips<br>TRT | FEI3                 | 0.25 μ<br>CMOS         | Front-end                              | ~28000                     |    |                    |       | BiMUX              | DN             | <b>/</b> ILL              | Multiplexor                       | ~8000<br>Bipolar design     |

|                                   | Module<br>Controller | 0.25 μ<br>CMOS         | Control                                | ~1800                      |    |                    |       | OpAmp              | DN             | <b>/</b> ILL              | Operational amplifier             | ~17000<br>Bipolar design    |

|                                   | VDC                  | 0.25 μ<br>CMOS         | VCSEL driver                           | ~500                       |    |                    |       | DAC                | DN             | <b>/</b> ILL              | 16-bit DAC<br>Control             | ~130                        |

|                                   | DORIC                | 0.25 μ<br>CMOS         | Timing and control receiver            | ~400                       |    |                    |       | SPAC slave         |                |                           | interface                         | ~2000                       |

|                                   | ABCD                 | DMILL                  | Front-end                              | ~50000<br>BiCMOS<br>design |    |                    |       | Configurat<br>SMUX | DMILL          |                           | Control<br>Digital<br>multiplexer | ~1600<br>~1600              |

|                                   | DORIC                | 0.35µ<br>BiCMOS        | Timing and control                     | ~4100                      |    |                    |       | Calibration logic  | DMILL          |                           | Glue logic                        | ~800                        |

|                                   | VDC                  | 0.35µ<br>BiCMOS        | VCSEL driver                           | ~8200                      |    |                    |       | SCA<br>controller  | 0.25 μ<br>CMOS |                           | Control                           | ~3200                       |

|                                   | ASDBLR               | DMILL                  | Amplifier-shaper-<br>discriminator     | ~38000<br>Bipolar design   |    |                    |       | Gain select        | CMOS           |                           | Control                           | ~13000                      |

|                                   | DTMROC               | 0.25 μ<br>CMOS         | Digitiser                              | ~19000                     |    |                    |       | Clock fan-         | CM CM          | 25 μ<br>4OS               | Clock driver                      | ~11000                      |

| Muon                              | ASIC                 | Technology             | Functionality                          | Quantity & remarks         |    |                    |       | DCU                |                | 5μ<br>105                 | Control                           | ~3200<br>CMS design         |

|                                   | ASD                  | 0.5 μ<br>CMOS          | Amplifier-shaper                       | ~5000                      |    |                    |       | HEC                | Ga             | As                        | Front-end<br>amplifier            | ~700<br>Inside liquid argon |

| MDT                               | AMT                  | 0.3 μ<br>CMOS          | Time to digital conv.                  | e to digital conv. ~15000  |    | Tile<br>Calorime   | eter  | TileDMU            |                | 5 μ<br>1OS                | Pipeline                          | ~256<br>Gate Array          |

| CSC                               |                      |                        |                                        |                            | 1  |                    |       |                    |                |                           |                                   | 1 0                         |

| CSC                               | ASM1 0.5 μ<br>CMOS   |                        | Preamplifier                           | ~1300                      | ļĻ | TGC                | ASD   |                    | Dinalar        |                           |                                   | ~81000                      |

|                                   | ASM2                 | 0.5 μ<br>CMOS          | Multiplexor                            | ~1300                      |    | HpT                |       | Bipolar<br>0.35 µ  |                | mplifier-shaper<br>rigger | ~800                              |                             |

|                                   | Clock driver         | 0.5 μ<br>CMOS          | Clock driver                           | ~200                       |    |                    | PP    |                    | CMOS<br>0.35 μ |                           | igger                             | ~15000                      |

|                                   | HAMAC-SC             | A DMILL                | Analogue memory                        | ~2600<br>Common with LAr   |    | TGC                | SLB   |                    | CMOS<br>0.35 μ |                           |                                   | ~3000                       |

| RPC                               |                      |                        |                                        |                            |    |                    |       |                    | CMOS           |                           | igger                             |                             |

| RPC                               | ASD<br>CMA           | GaAs<br>0.18 μ<br>CMOS | Amplifier-shaper<br>Coincidence matrix | ~47000<br>~3300            |    |                    | JRC   |                    | 0.35 μ<br>CMOS | JŢ                        | AG controller                     | ~1400                       |

Integrated Circuits -- M. Garcia-Sciverers

AT THIS SITE IN 1959, DR. ROBERT NOYCE OF FAIRCHILD SEMICONDUCTOR CORPORATION INVENTED THE FIRST IN-TEGRATED CIRCUIT THAT COULD BE PRODUCED COMMER-CIALLY. BASED ON "PLANAR" TECHNOLOGY, AN EARLIER FAIRCHILD BREAKTHROUGH, NOYCE'S INVENTION CONSISTED OF A COMPLETE ELECTRONIC CIRCUIT INSIDE A SMALL SILICON CHIP. HIS INNOVATION HELPED REVOLUTIONIZE "SILICON VALLEY'S" SEMICONDUCTOR ELECTRONICS IN-DUSTRY, AND BROUGHT PROFOUND CHANGE TO THE LIVES OF PEOPLE EVERYWHERE.

CALIFORNIA REGISTERED HISTORICAL LANDMARK NO. 1000 PLAQUE PLACED BY THE STATE DEPARTMENT OF PARKS AND RECREATION IN COOPERATION WITH INTEL COR-PORATION, AUGUST 9, 1991.

Jan 31, 2018

- Here: Segre, Chamberlain get Nobel prize to antiproton discovery

- There: The CERN PS produced first beam (28 GeV)

Integrated Circuits -- M. Garcia-Sciverers

## **HEP need for ASICs**

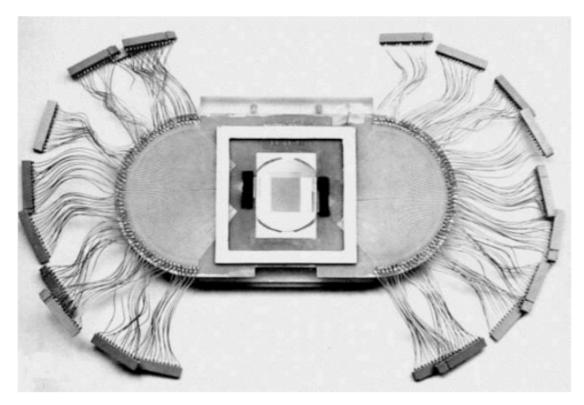

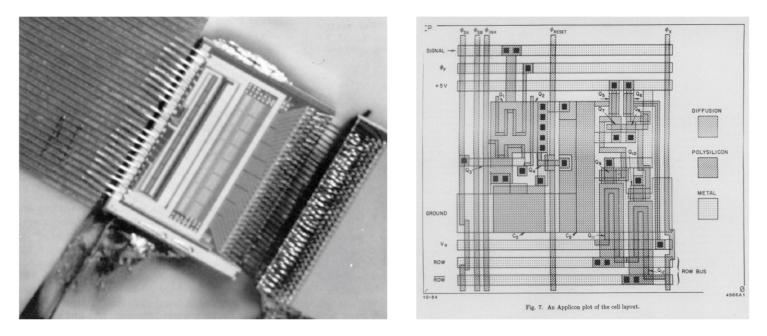

#### NA11, CERN 1981. Silicon strip sensor with discrete readout

NIM205 (1983) 99

=> Special connection between silicon detectors and ASICs

- Stanford / SLAC's NMOS Microplex (left) and Microstore (right)

- Walker, Parker, Hyams, Shapiro, "Development of High Density Readout for Silicon Strip Detectors," NIM 226 (1984).

- Walker, Chae, Shapiro, Larsen, "Microstore the Stanford Analog Memory Unit," IEEE TNS NS-32, No 1. Feb. 1985

#### Sherwood's IEEE outstanding achievement award in 2015

- The SVX chip was likely the first CMOS ASIC for physics. It offered improved amplification, auto-zeroed offset and leakage, sparse data scanning + nearest-neighbor logic, etc. (Kleinfelder, 1988).

- The SCA Switched Capacitor Array introduced a DRAM-like architecture for high density and low power, with rail-to-rail operation (Kleinfelder, 1988).

Stuart holding microplex wafers at HEPIC 2017

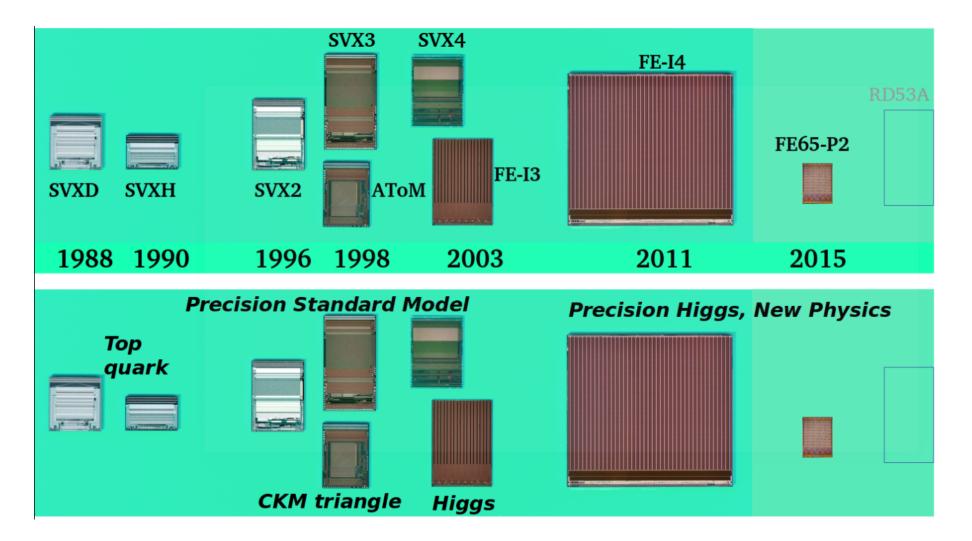

## Silicon detector chips at LBL

IIIÌ

.....

BERKELEY

# **Special Place of Berkeley**

2012

inte

Ivy Bridge

#### A few snippets

The 1970s-pioneered contributions to computer-aided design for microelectronics, the best-known being the SPICE program, were led by Professors D. O. <u>Pederson</u>, E. S. <u>Kuh</u>, and R. A. Rohrer. Industry-leading firms, including Cadence and Synopsys, were founded by graduates to commercialize design tools for microelectronics. A Berkeley team led by Profs. R. W. <u>Brodersen</u>, P. R. <u>Gray</u>, and D. A. <u>Hodges</u> invented mixed-signal MOS integrated circuits, combining precision analog-digital conversion and switched-C filters with high-density digital circuits.

Dr. Chenming Hu has been called the <u>Father of 3D Transistor</u> for developing the <u>FinFET</u> in <u>1999</u>. (Steve Holland's thesis advisor)

Steve Holland developed fully depleted CCD's in the 90's. following a suggestion from Dave Nygren This used the Microsystems Lab in bldg. 70A, which is an on-site IC fab.

In the late 80's Dave Nygren initiated research aimed at developing "smart-pixel arrays" for SSC. This work led to the ATLAS pixel readout system based on the column drain architecture

- https://www.youtube.com/watch?v=JDROPMoNZpk

- https://www.youtube.com/watch?v=3m4WmYObxzY

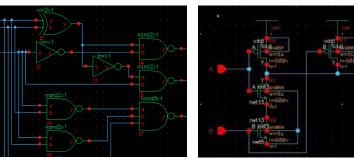

# How are IC' are designed?

#### Flow, Methodology.

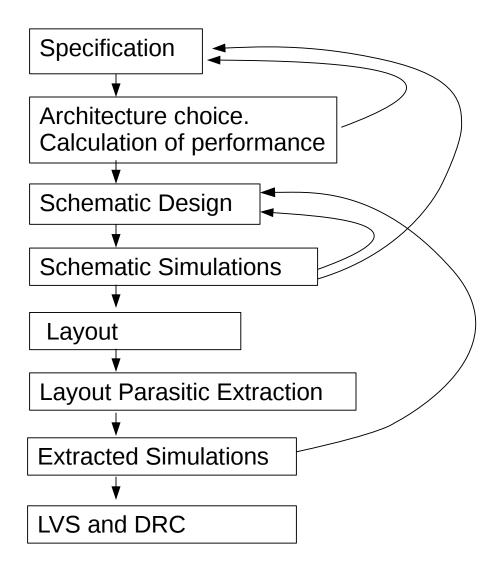

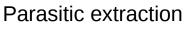

#### Full Custom Flow

# How are IC' are designed?

#### Flow, Methodology.

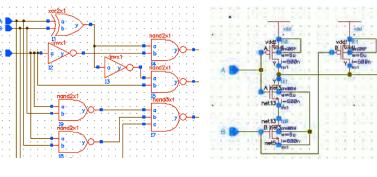

#### **Full Custom Flow**

PortB

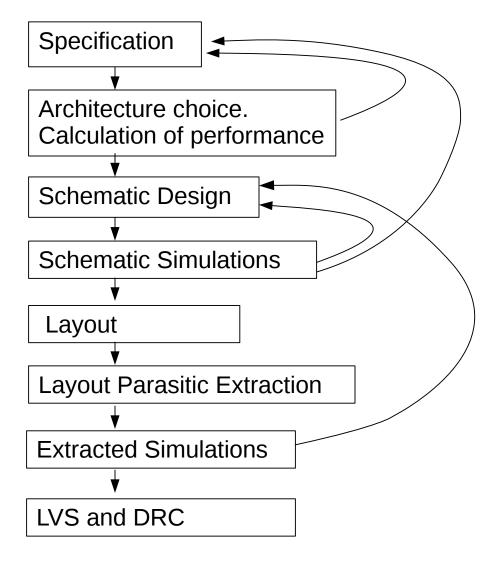

# How are IC' are designed?

#### Flow, Methodology.

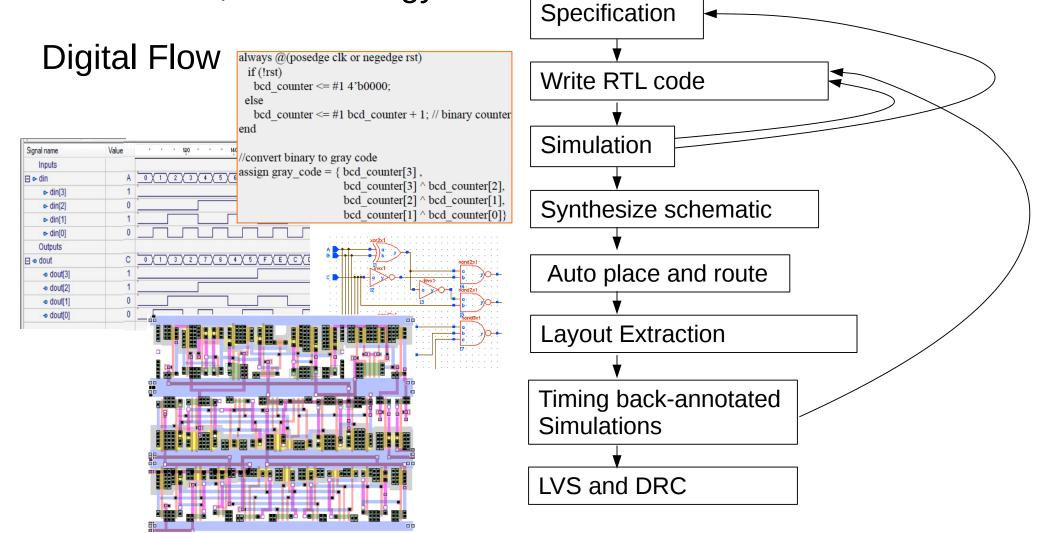

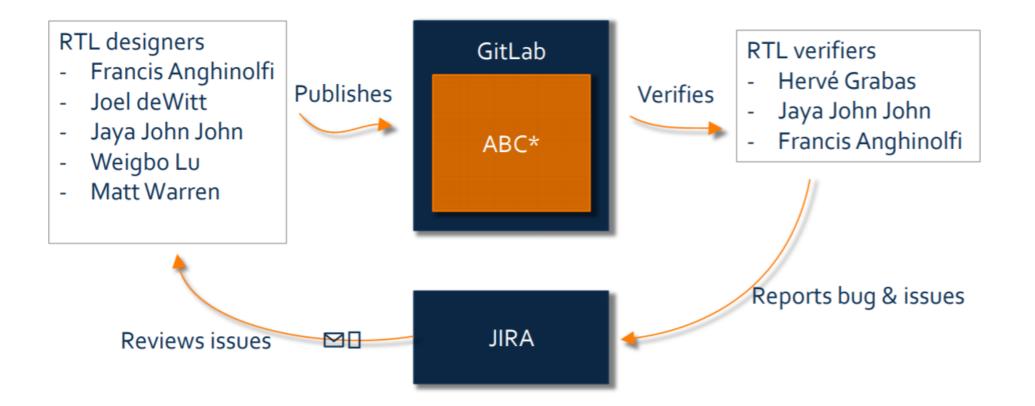

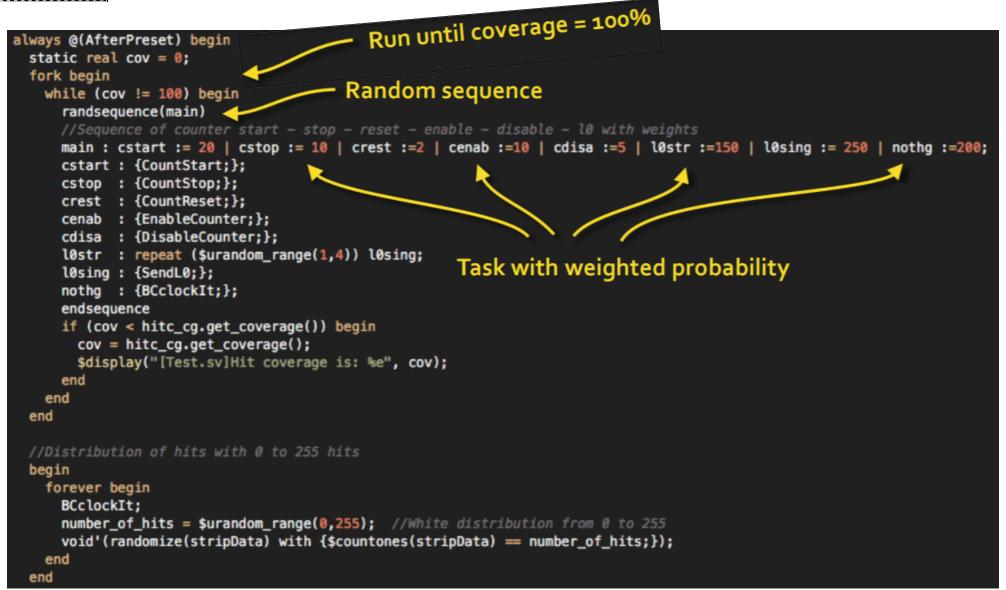

RTL = Register Transfer Level. Written in a high level description language VHDL, Verilog.

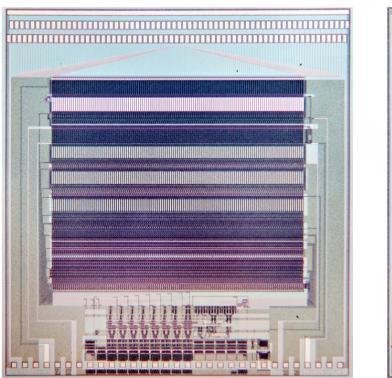

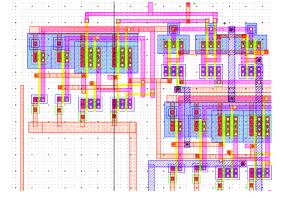

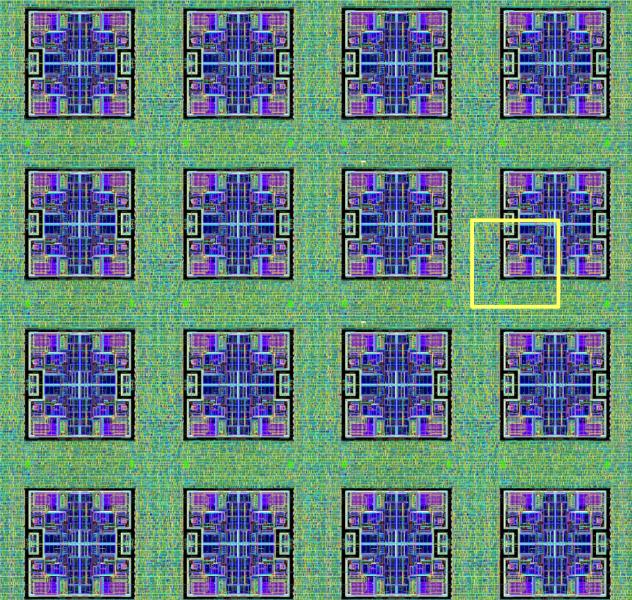

## One RD53A Chip Core

One flat synthesized circuit Each pixel is different !

Whole block is stepped and repeated

~ 200k transistors Size chosen so it CAN be SPICE simulated

(routing dominated re: metal stack)

16 yrs ago Full custom including logic

8 yrs ago Full custom layout With synthesized logic inserts Now Full digital flow With analog inserts

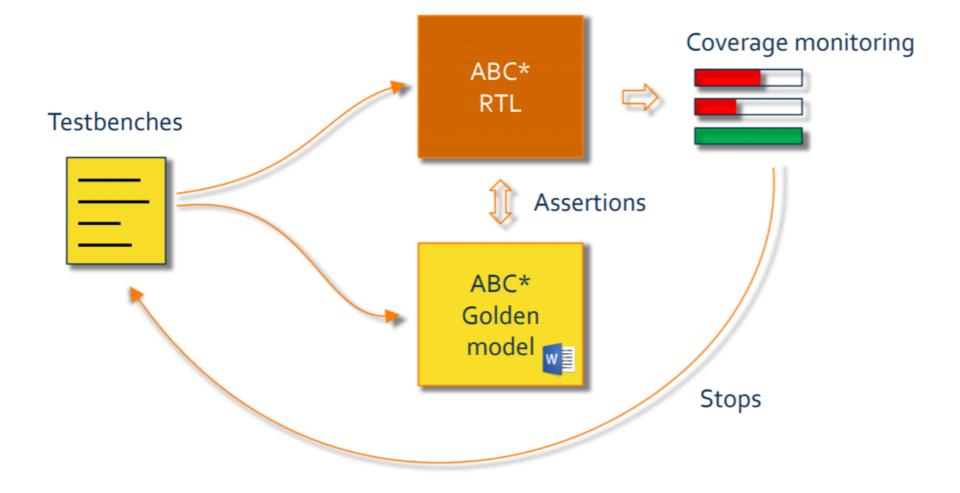

- Basically, how to ensure that an IC design sent to fabrication will result in a working chip.

- Integration of individual elements (circuits) into a full chip

- Validation that the full chip is bug free

- Goal: remove all possibility for human error

- Digital is compiled code

- Analog is hand drawn by a human

Which do you think can be more reliably automatically verified?

## Code segment example: counters

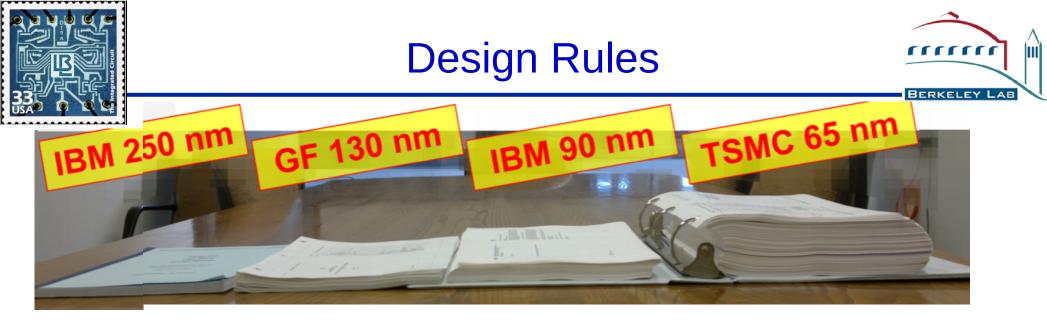

- Process is like a "build your own" sandwich:

- Pre-defined as: bread, dressing, cheese, meat, veggies

- You choose type of bread, dressing, cheese, meat, veggies, but not

- order (bread goes outside and dressing goes on bread),

- sizes and amounts, etc.

- Design rules specify layers, layer properties, restrictions, etc.

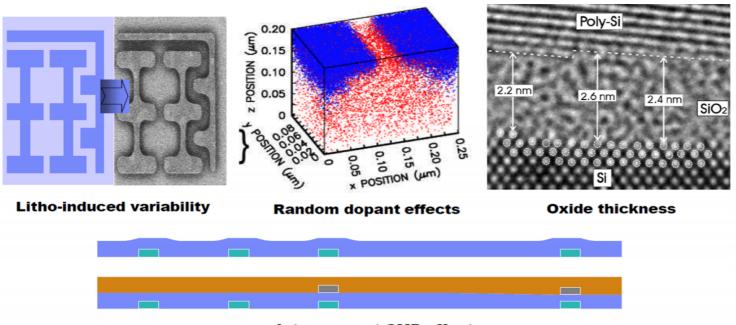

# Variability (mismatch)

Interconnect CMP effects

Logically these get worse the smaller the feature size Design rules mitigate them. Would be overwhelming without complex rules. Eg. Density :

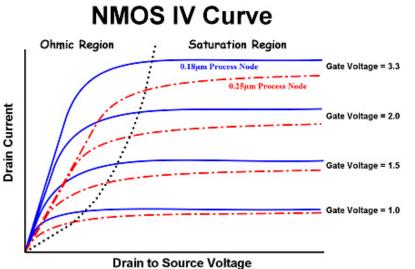

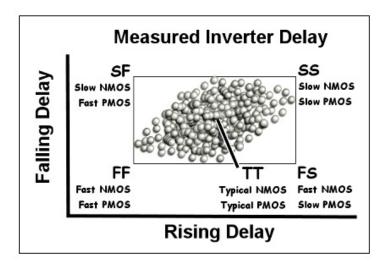

# **Simulation Models and Corners**

- Parametrized transistor response for analog simulation

- Parametrized gate delays & thresholds for digital simulation

- Parameters: size, voltage, temperature, process corners,...

- What about using transistors outside model parameters?

- Two approaches:

- De-rate existing parameters. For example model at lower voltage

- Make your own corner models

- Second one is more work, but really the only way to take full advantage of very powerful digital design tools

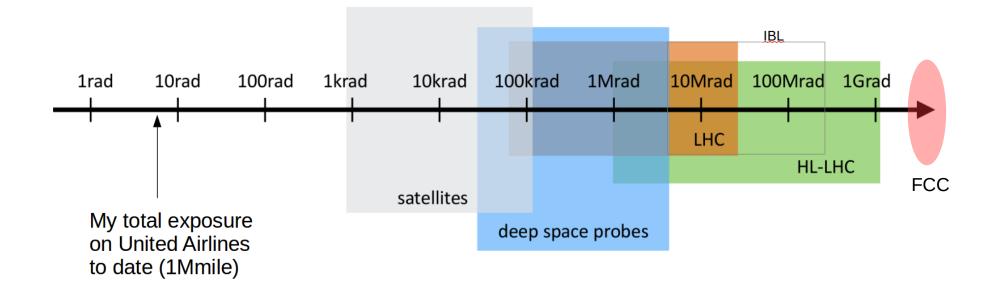

Radiation

#### We need to model its effect

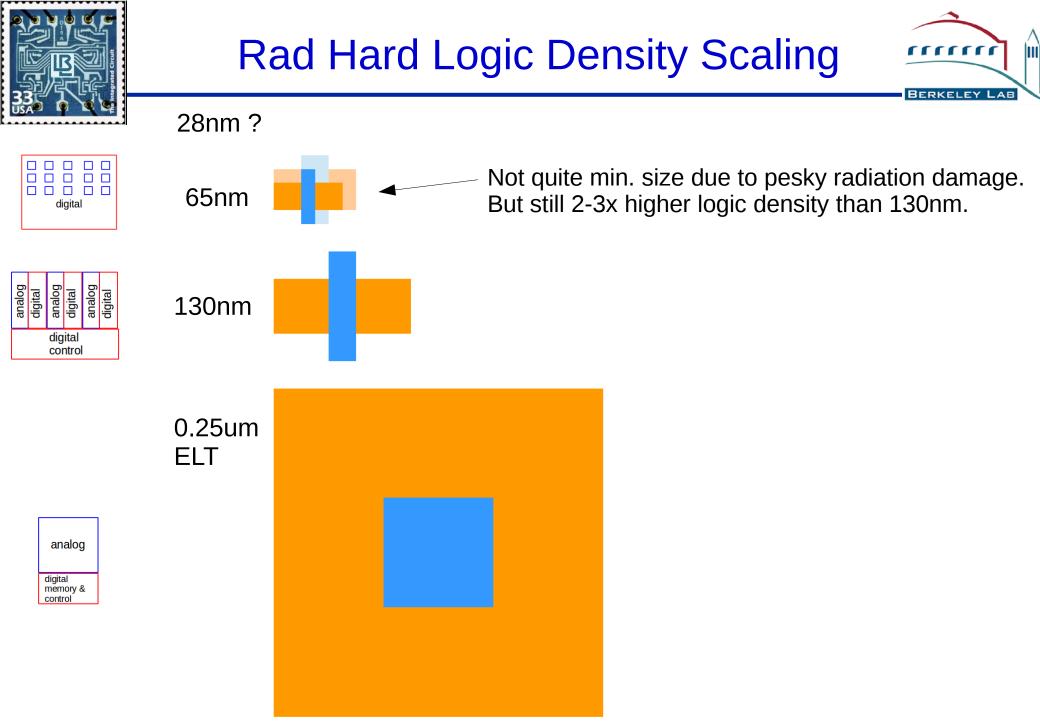

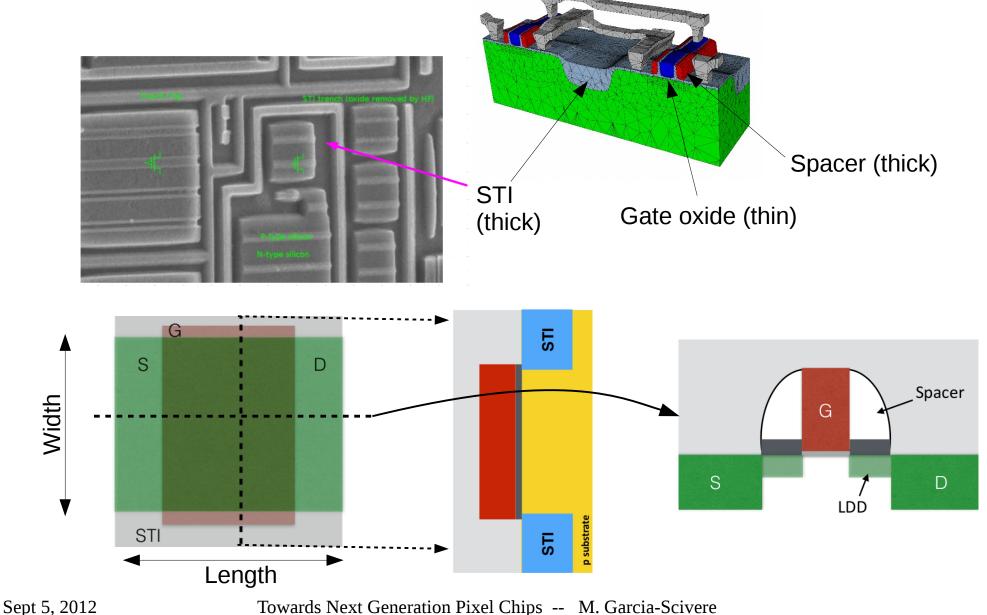

### Radiation damage is an oxide affair STI, Gate, Spacer

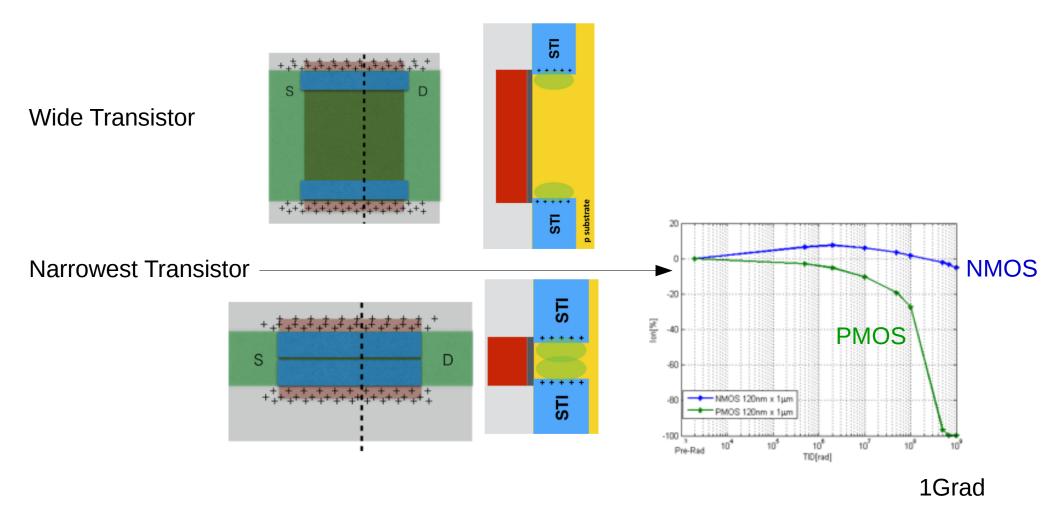

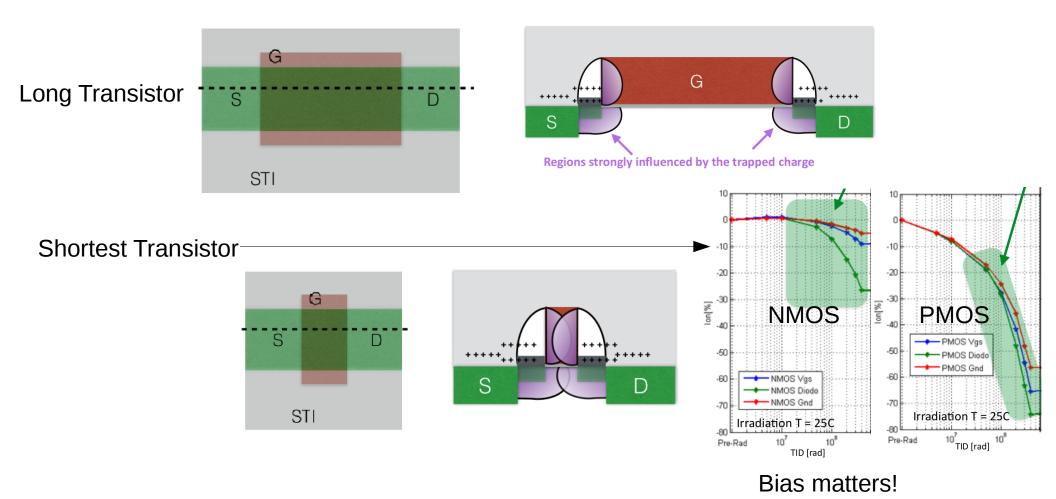

#### **Radiation Induced Narrow Channel Effect**

F. Faccio and G.Cervelli, "Radiation induced edge effects in deep submicron CMOS transistors", IEEE Trans. Nucl. Science, Vol.52, N.6 (2005) pp.2413-2420 http://dx.doi.org/10.1109/TNS.2005.860698

#### Towards Next Generation Pixel Chips -- M. Garcia-Scivere

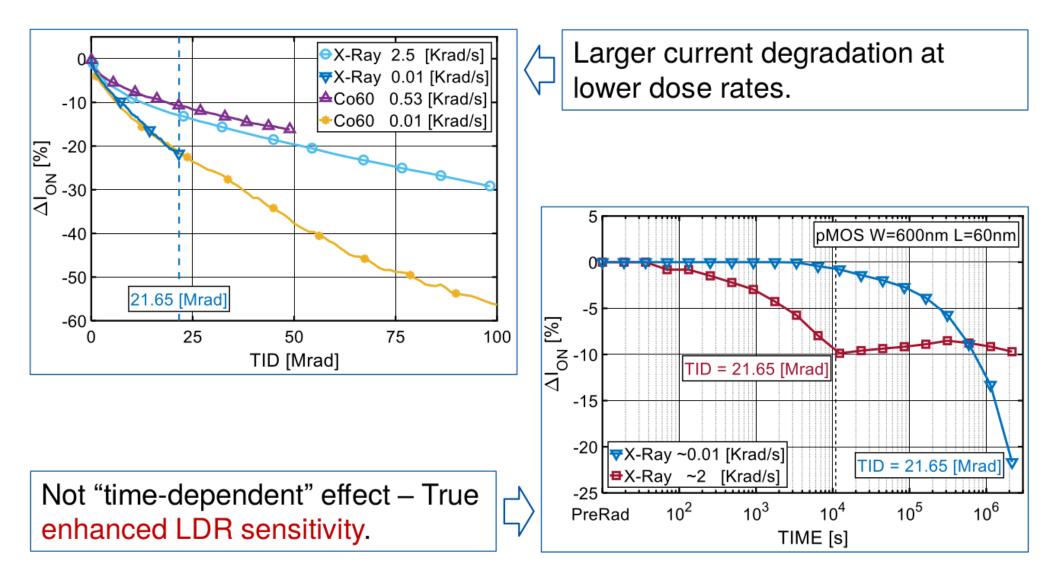

#### Radiation Induced Short Channel Effect

F. Faccio et al., "Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs," IEEE Trans. Nucl. Science, Vol.62, N.6 (2015) http://dx.doi.org/10.1109/TNS.2015.2492778

Towards Next Generation Pixel Chips -- M. Garcia-Scivere

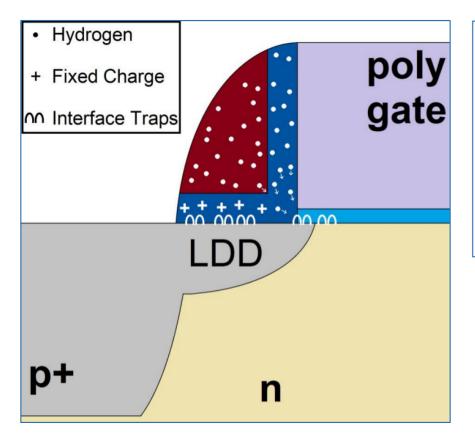

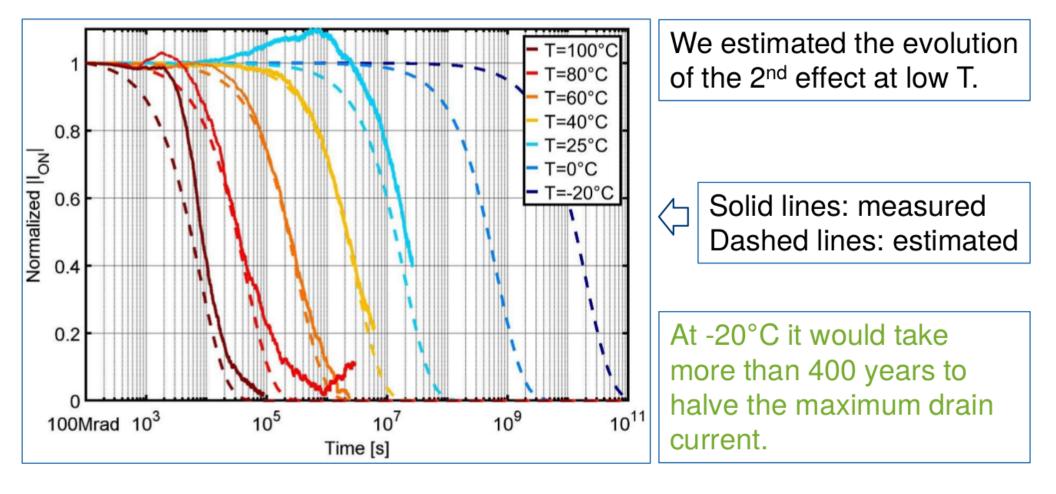

# Some understanding of complex mechanisms

F. Faccio, et. al, "Influence of LDD spacers and h+ transport on the total-ionizing-dose response of 65 nm mosfets irradiated to ultra-high doses," Presented at the 2017 NSREC.

#### 3-stage process:

- 1. Ionization in the spacers.

- 2. Transport of H<sup>+</sup> from the spacers to the channel region.

3. De-passivation of Si-H bonds at the interface with the gate oxide.

✓ Large threshold voltage shift.

**rrr**r

lm)

Towards Next Generation Pixel Chips -- M. Garcia-Scivere

....

lm)

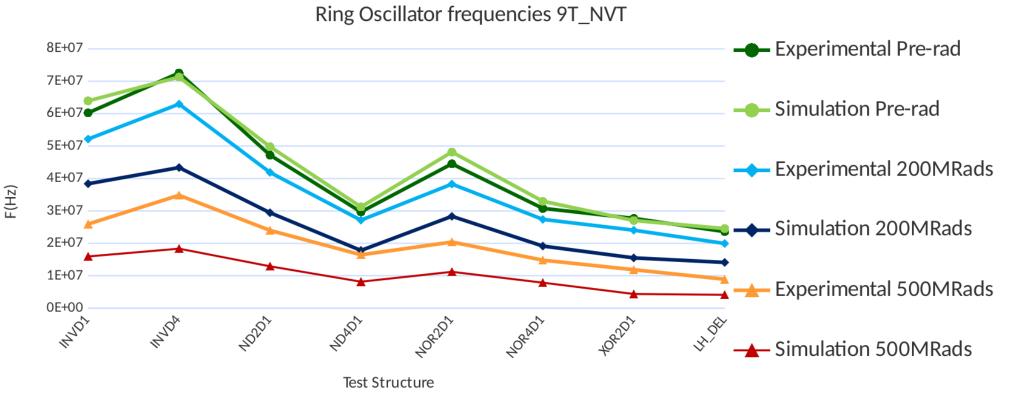

## Digital switching is safe: Data-simulation comparison

- Comparison of models used in RD53A chip with test chip data.

- Ring oscillator frequency is sensitive to TID effects

- Different logic cells can be used to make ring oscillator test structures

- Models were built from single transistor data under DC worst case bias.

- A switching transistor is less vulnerable. We see 2x less damage.

Integrated Circuits -- M. Garcia-Sciverers

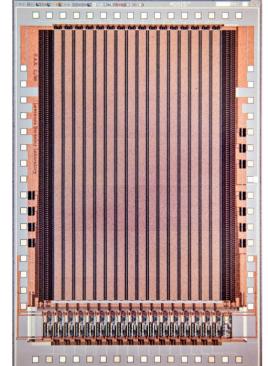

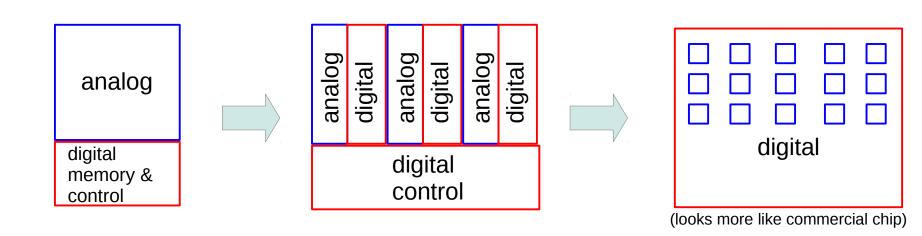

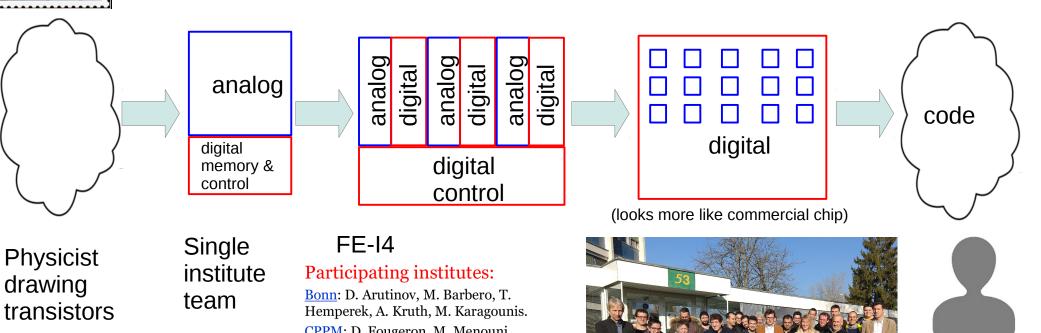

# Shift in IC Design Approach

Your pic here

....

BERKELEY

IIIÌ

| FE-I4                                                                           |

|---------------------------------------------------------------------------------|

| Participating institutes:                                                       |

| <u>Bonn</u> : D. Arutinov, M. Barbero, T.<br>Hemperek, A. Kruth, M. Karagounis. |

| CPPM: D. Fougeron, M. Menouni.                                                  |

| Genova: R. Beccherle, G. Darbo.                                                 |

| LBNL: S. Dube, D. Elledge, M. Garcia-                                           |

| Sciveres, D. Gnani, A. Mekkaoui.                                                |

| Nikhef: V. Gromov, R. Kluit, J.D. Schipper                                      |

Nov. 2017 RD53 meeting, CERN

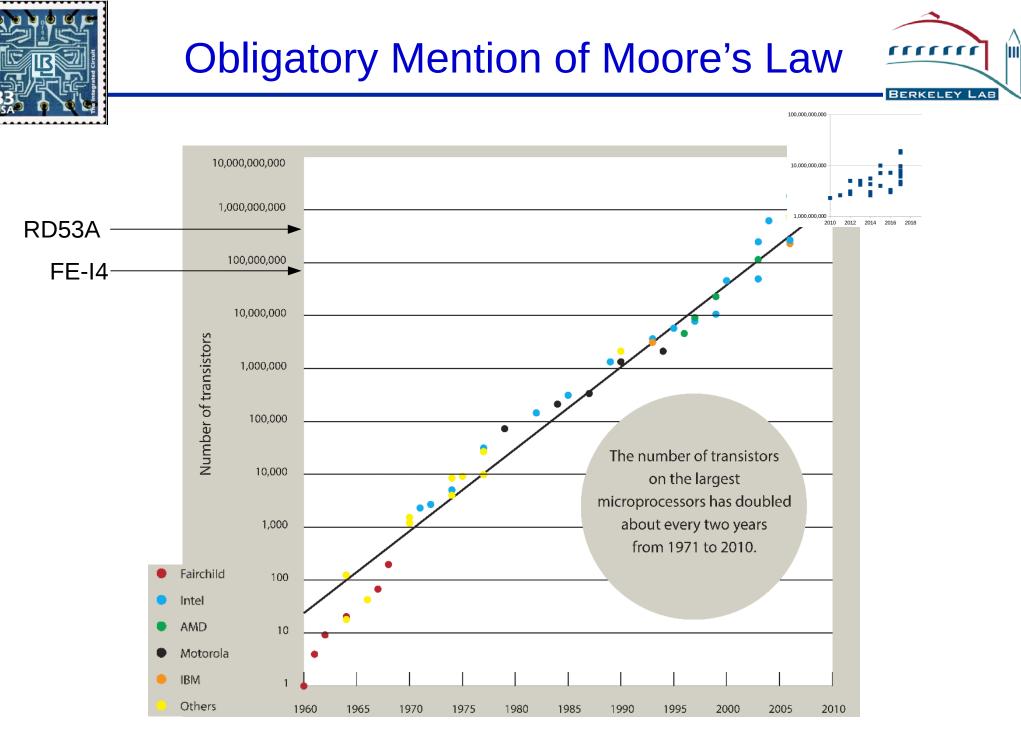

Commercial style design and validation 10<sup>9</sup> transistor Chips work the first time

Integrated Circuits -- M. Garcia-Sciverers

- This was not a practical or quantitative lecture on IC desing

- Presented a flavor of what you could learn more about

- ASIC's and/or microfabrication are essential to almost every experiment

- Maybe one should know something about this

- Should there be a real IC design lab course for physics students?

- (end product is a tape-out of your very own design IC)

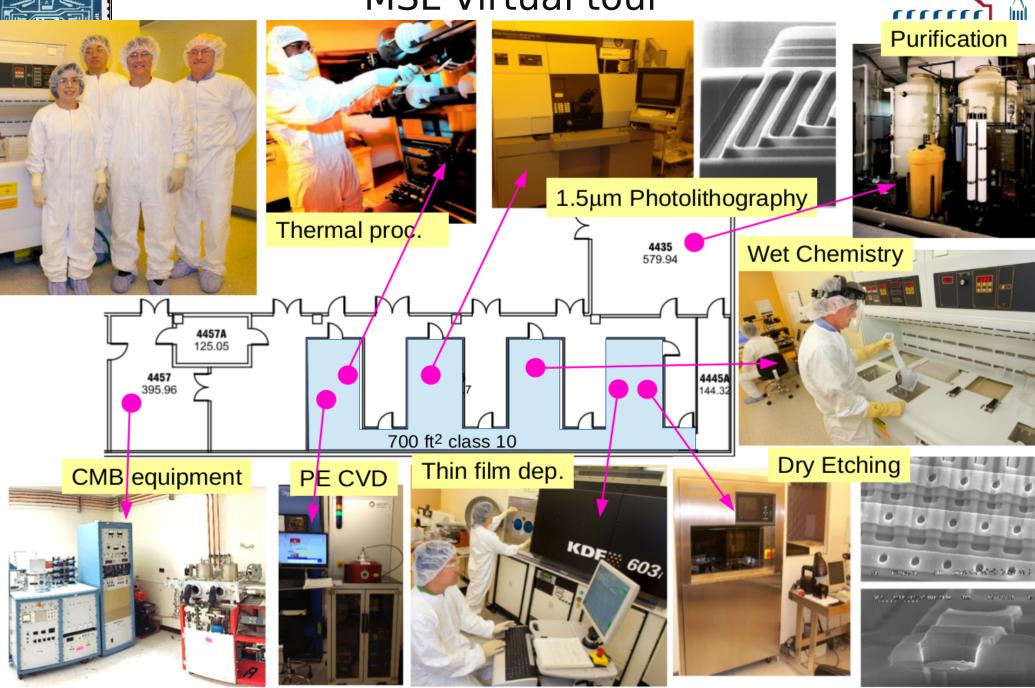

#### **MSL** Virtual tour