# ITKPIX 101

UNIVERSITY OF CALIFORNIA

ITk Pixel Module QC Workshop Not a lecture - 13.01.25

Timon Heim - LBNL

- I will/can not be exhaustive, happy to go into more detail if questions come up

- Here I compiled information I would consider useful at the user-level

- I will make generalizations that are not fully correct but are communicating the right understanding

- The slides are "incomplete" if viewed offline as I will make use of the white board

- I explain better when I can see what is unclear

- Most of the information is leveraged from the manual and paper:

- Manual: <u>https://cds.cern.ch/record/2890222</u>

- Paper: <u>https://cds.cern.ch/record/2898416</u>

### Disclaimer

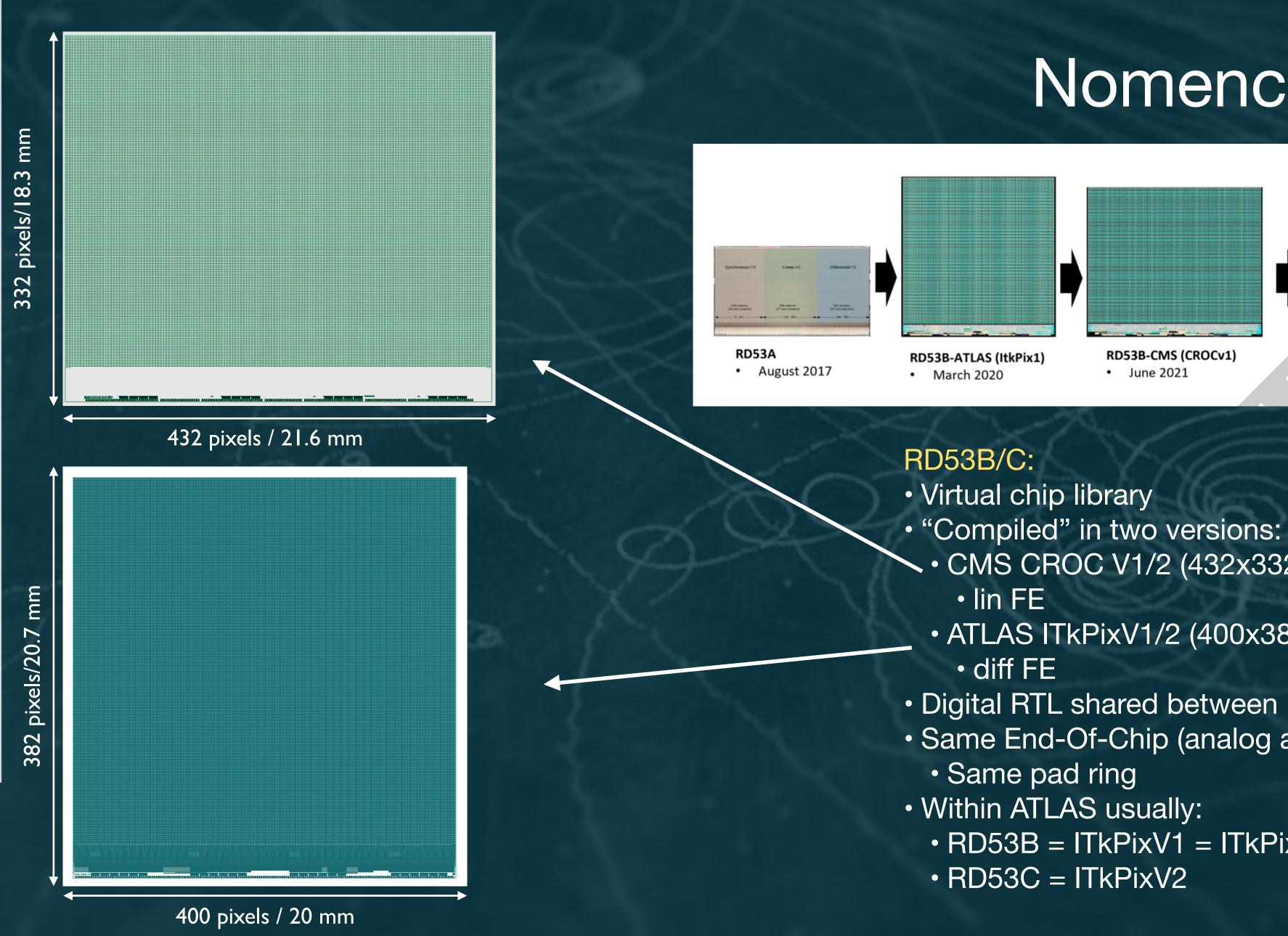

### Nomenclature

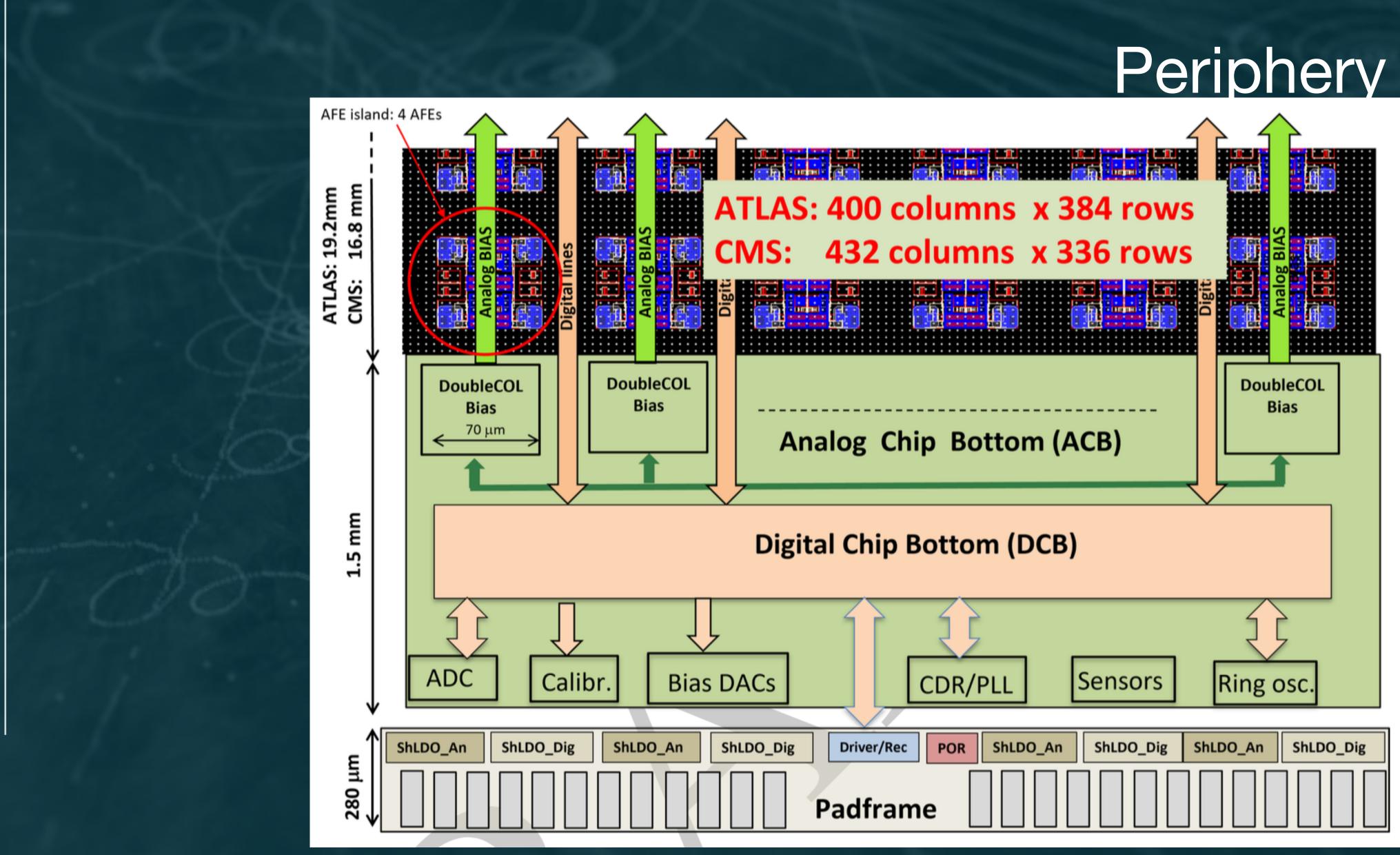

RD53C-ATLAS (ItkPix2) • March 2023

RD53C-CMS (CROCv2) October 2023

- CMS CROC V1/2 (432x332 pixels)

### • ATLAS ITkPixV1/2 (400x384 pixels)

- Digital RTL shared between both chips

- Same End-Of-Chip (analog and digital) for both chips

- - RD53B = ITkPixV1 = ITkPixV1.1 != ITkPixV1.0

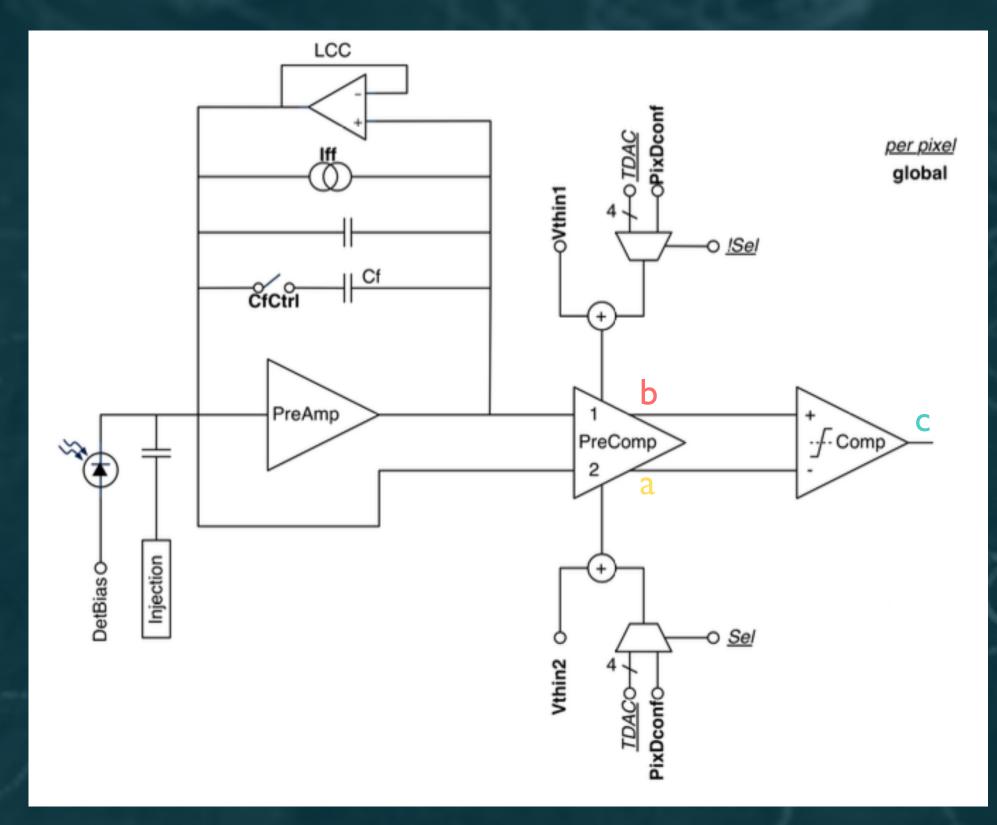

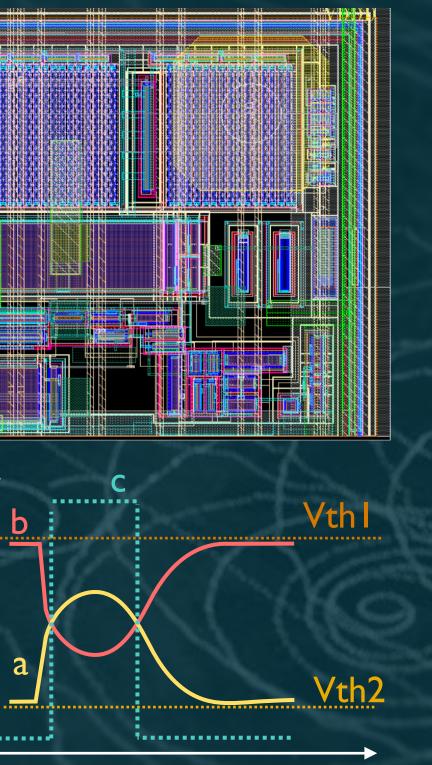

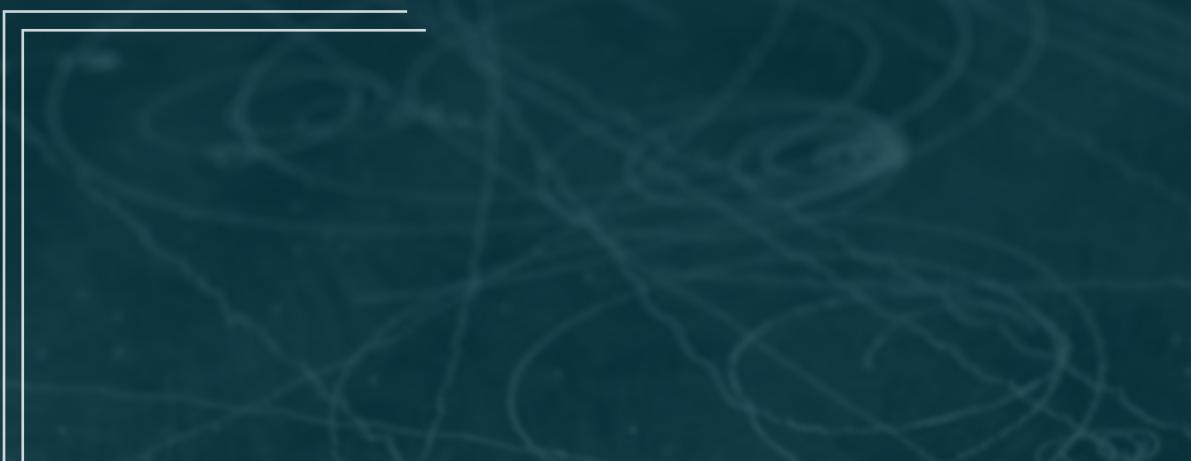

Charge Sensitive Amplifier:

- Straight cascode design

- Global settings for I<sub>f</sub> (8-bit DAC)

- Selectable gain

Timon Heim

## **Differential Front-End**

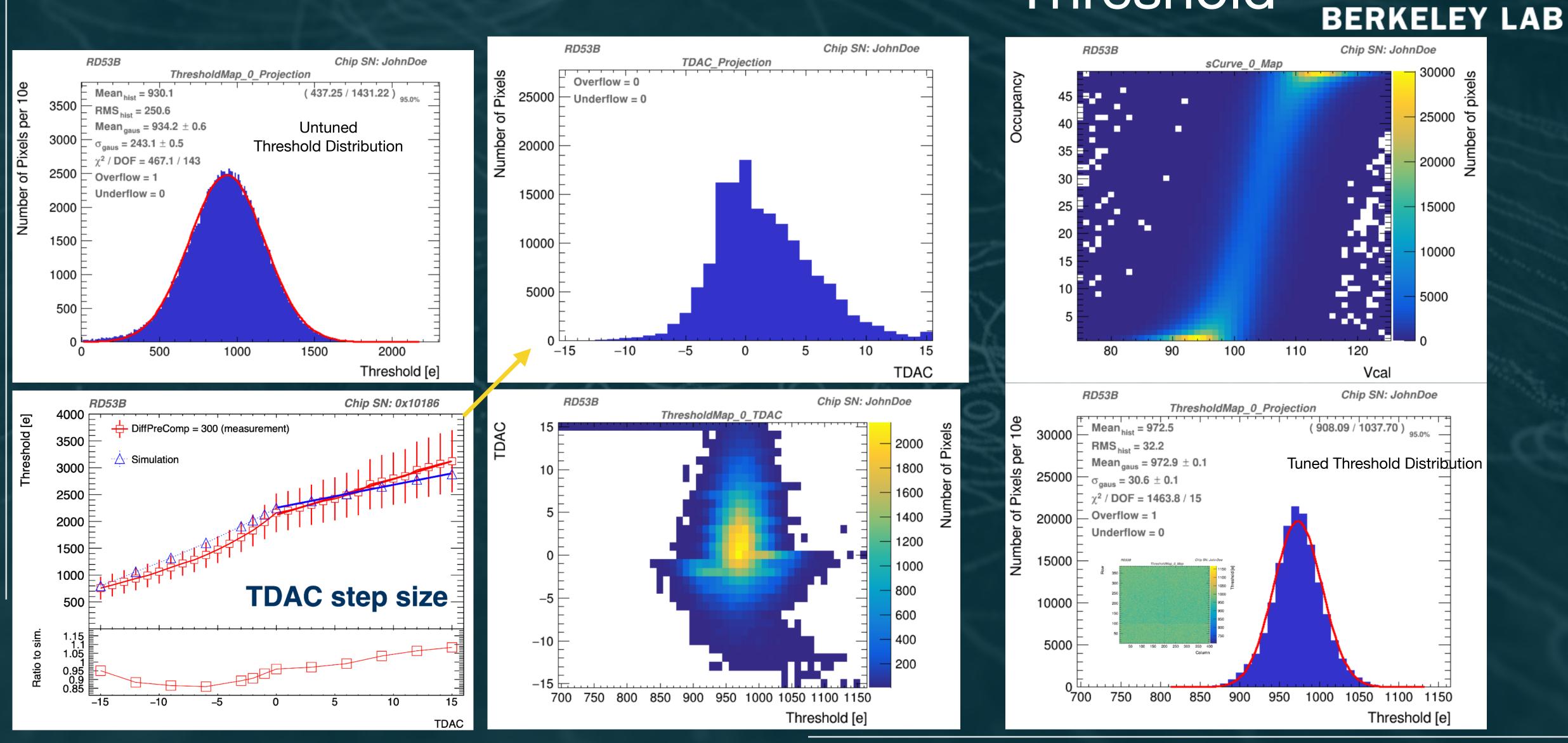

### Two Stage Comparator:

- Differential design

- Global 8-bit threshold DAC

- Two per pixel 4-bit threshold DACs

- Optimised for low threshold operation

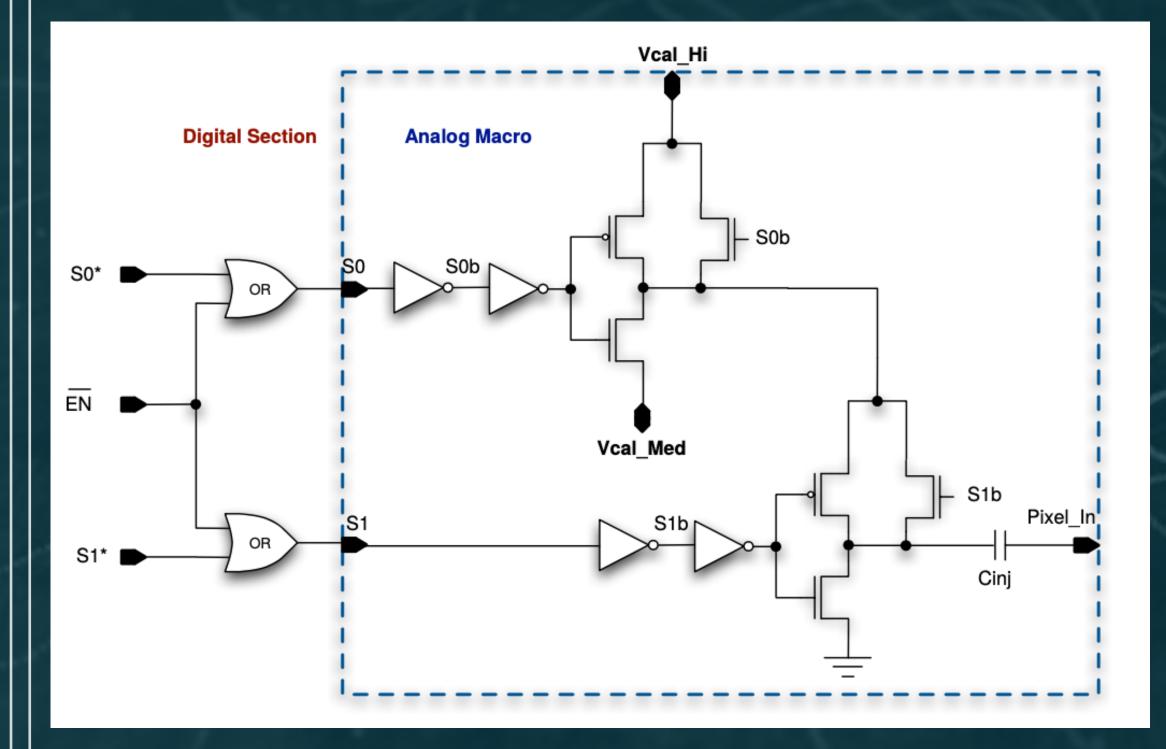

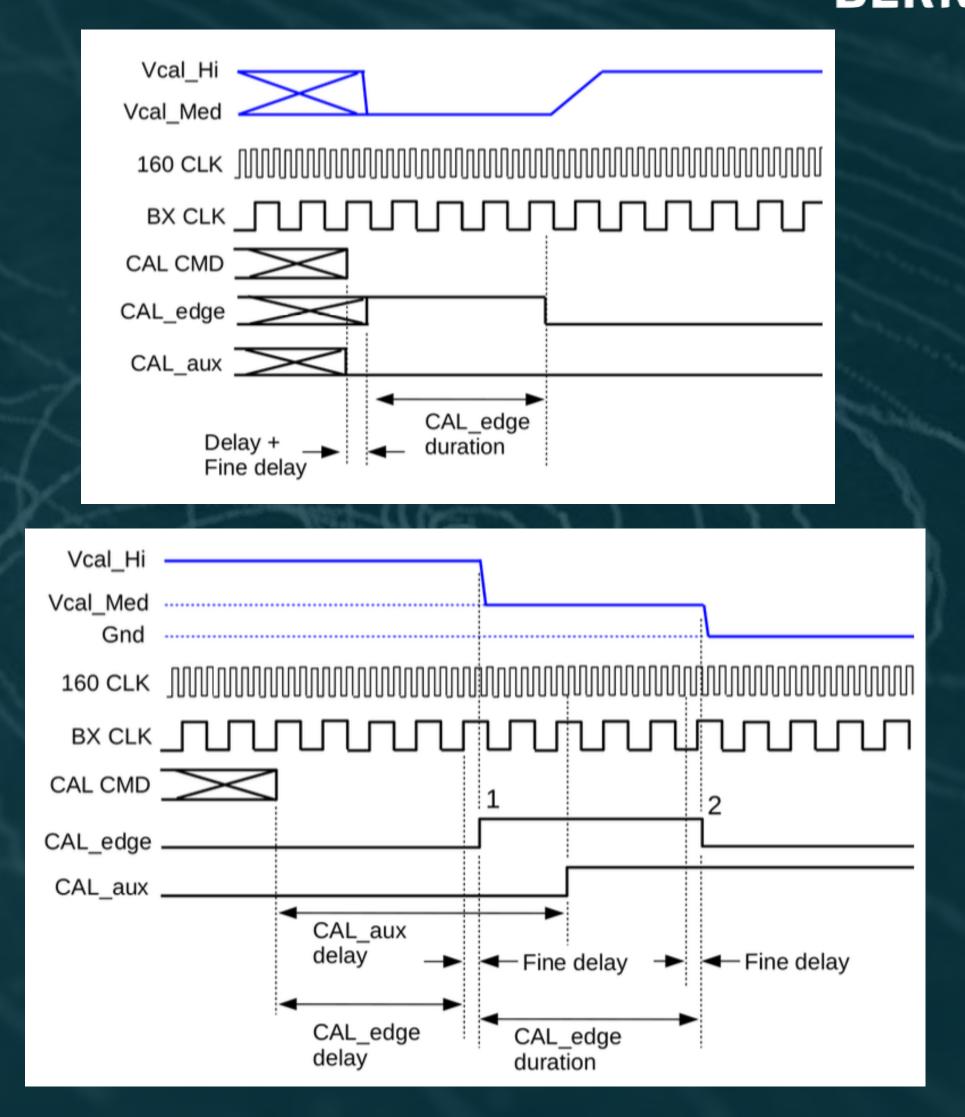

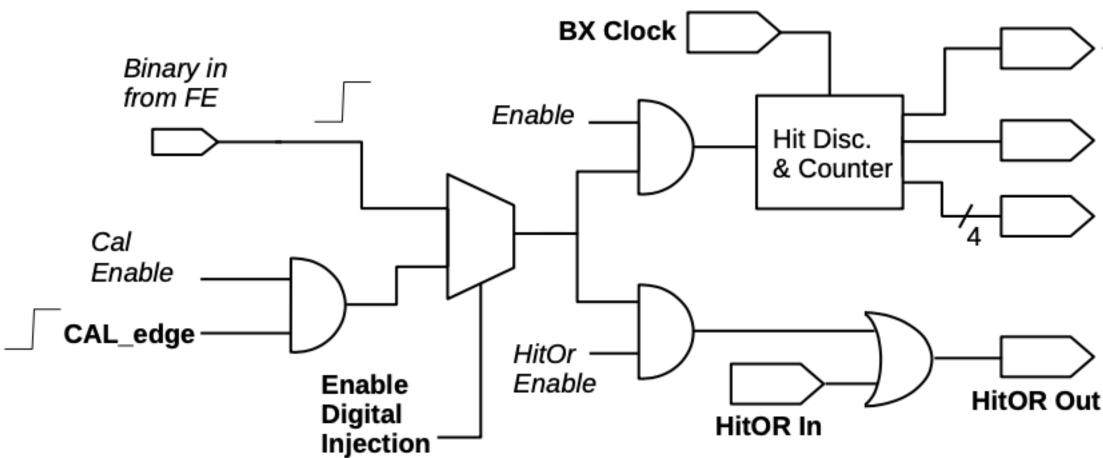

### $SO = CAL_edge OR CAL_aux$ $S1 = \overline{CAL}_{edge} AND CAL_{aux}$

Timon Heim

### Injection

FFFFF

## Generic AFE

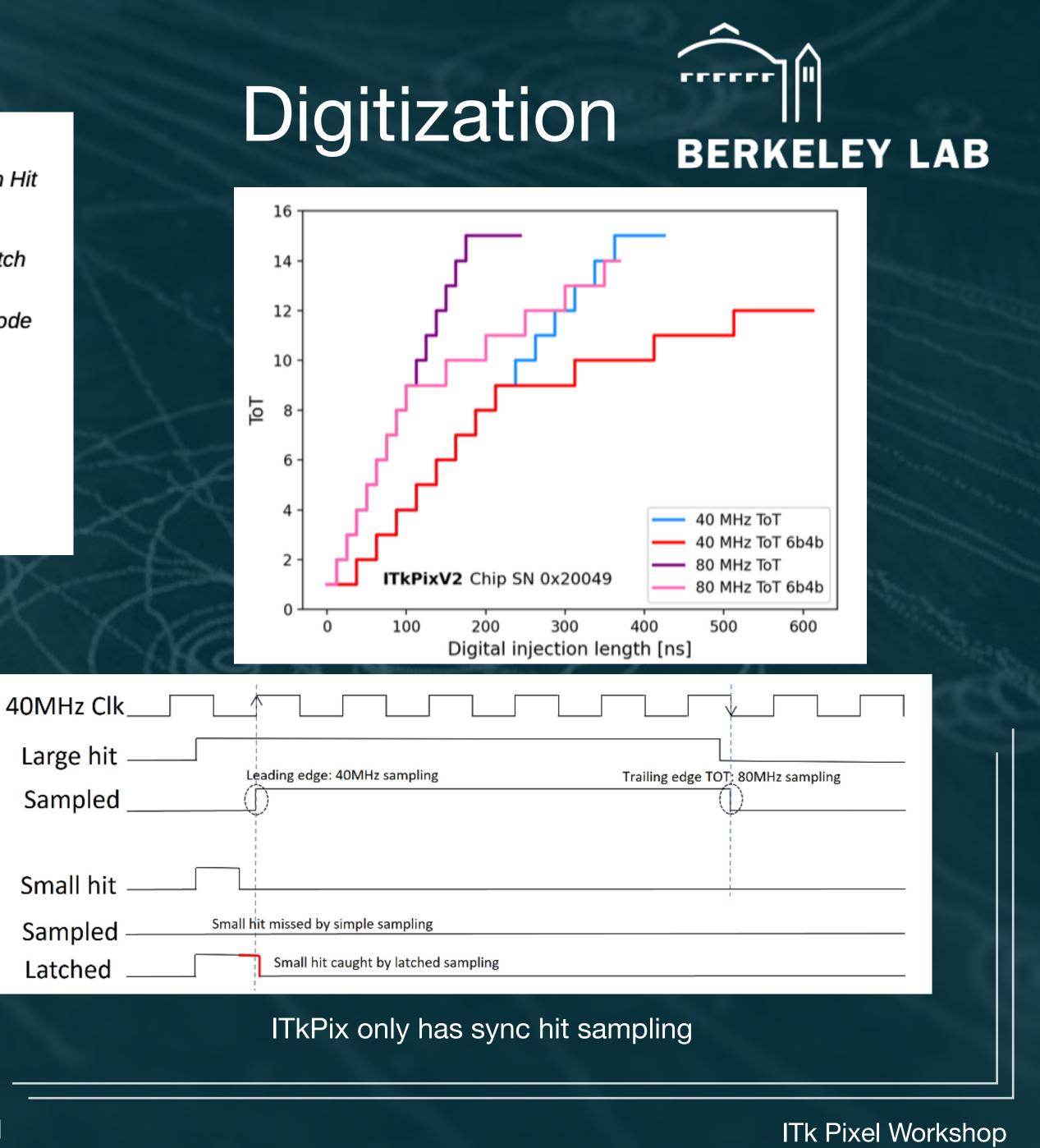

ToT (25.0 ns)

Timon Heim

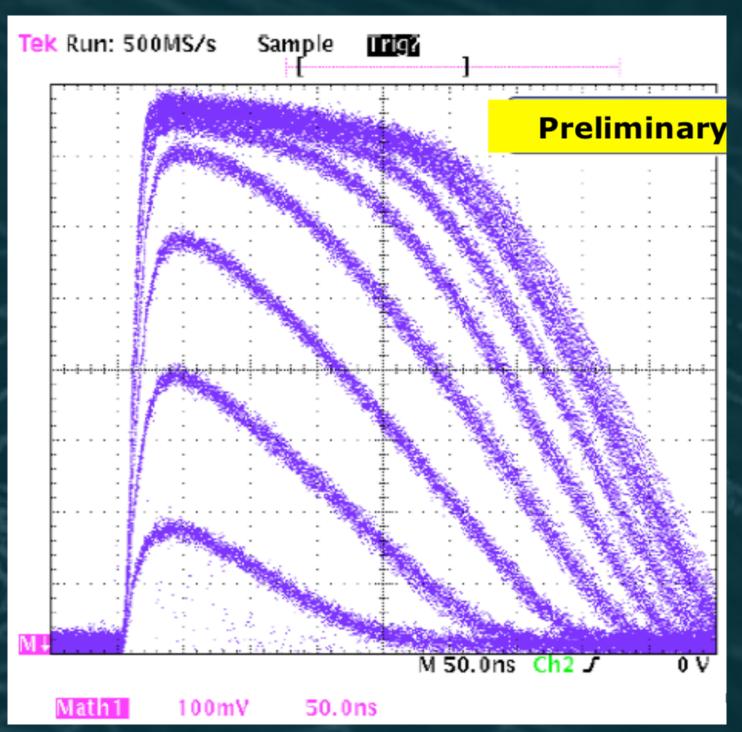

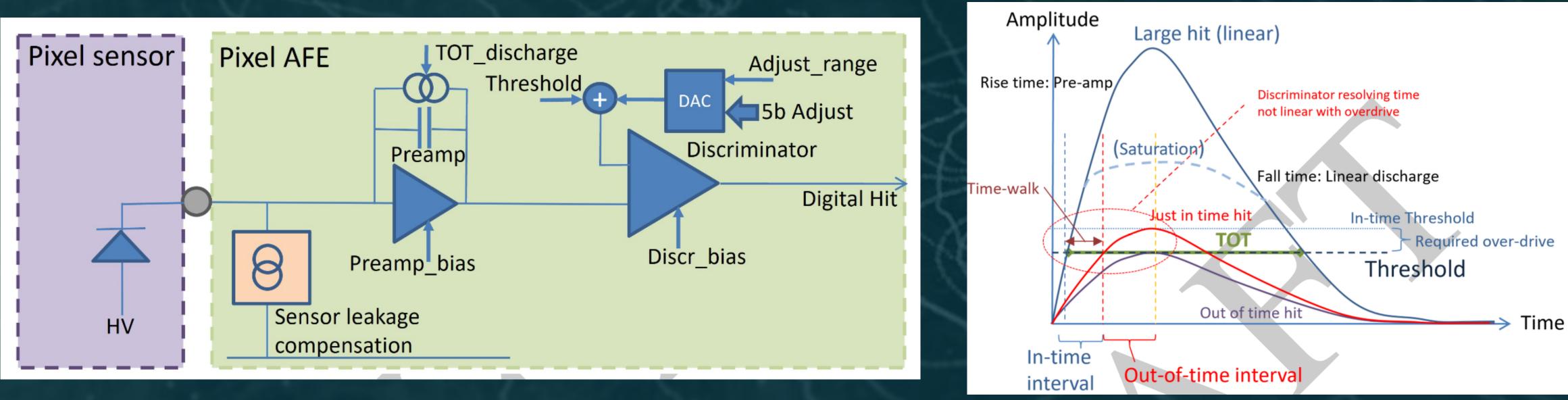

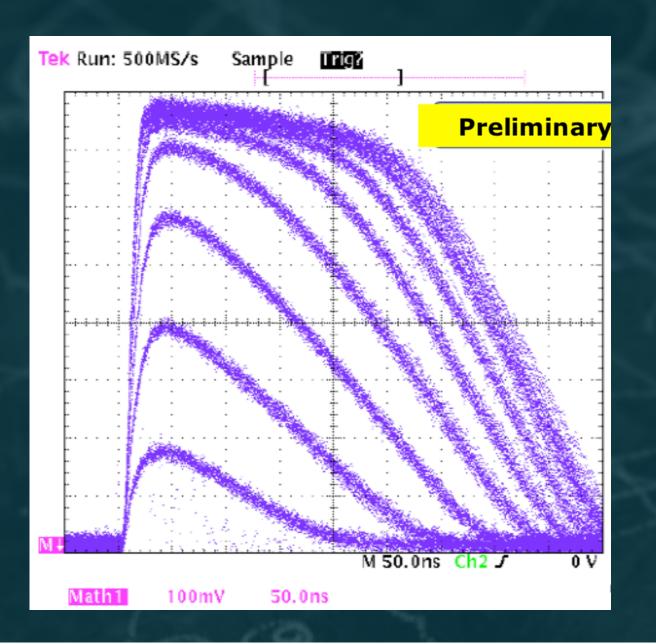

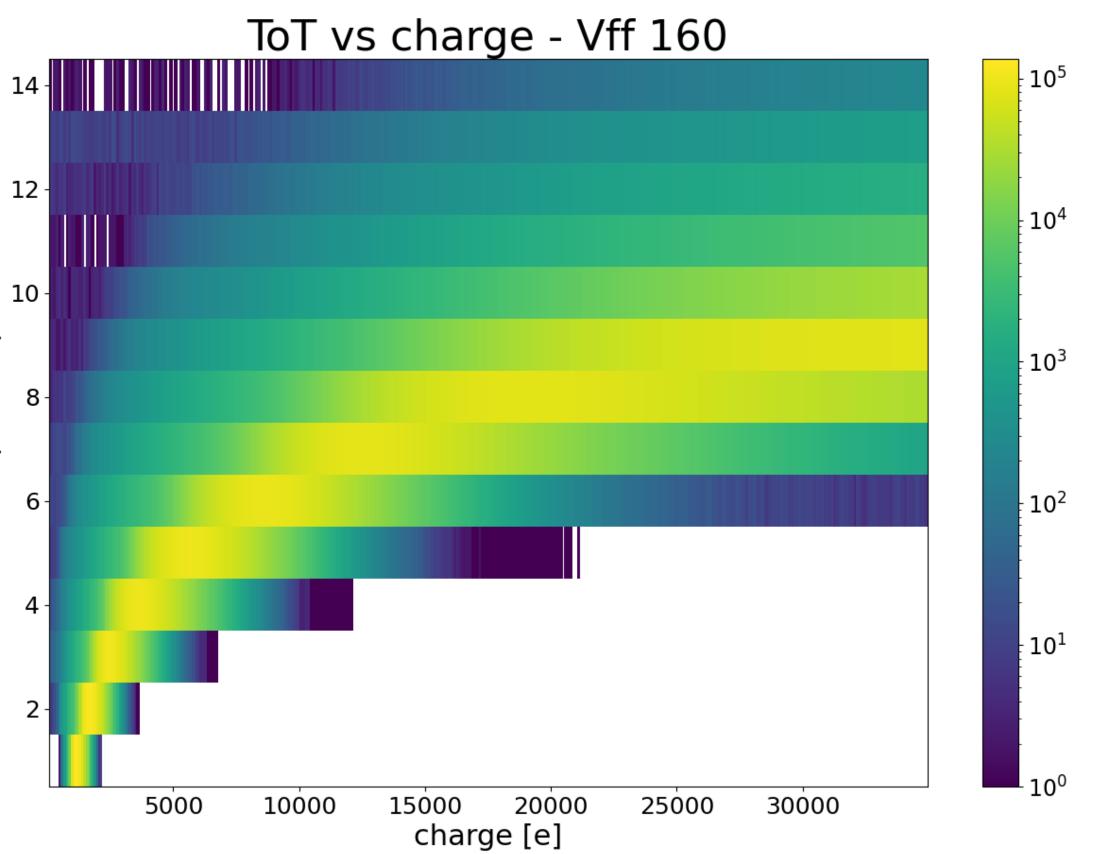

## Diff FE ToT Response

### Threshold

FFFFF

| Output True ToT bin (low edge) [BX] |             |            |              |            |  |  |  |

|-------------------------------------|-------------|------------|--------------|------------|--|--|--|

| Output<br>4-bit                     | 40 MHz      |            | 80 MHz speed |            |  |  |  |

| code                                | 4-bit (DEF) | 6-to-4 bit | 4-bit        | 6-to-4 bit |  |  |  |

| 0                                   | 0           | 0          | 0            | 0          |  |  |  |

| 1                                   | 1           | 1          | 0.5          | 0.5        |  |  |  |

| 2                                   | 2           | 2          | 1            | 1          |  |  |  |

| 3                                   | 3           | 3          | 1.5          | 1.5        |  |  |  |

| 4                                   | 4           | 4          | 2            | 2          |  |  |  |

| 5                                   | 5           | 5          | 2.5          | 2.5        |  |  |  |

| 6                                   | 6           | 6          | 3            | 3          |  |  |  |

| 7                                   | 7           | 7          | 3.5          | 3.5        |  |  |  |

| 8                                   | 8           | 8          | 4            | 4          |  |  |  |

| 9                                   | 9           | 12         | 4.5          | 6          |  |  |  |

| 10                                  | 10          | 16         | 5            | 8          |  |  |  |

| 11                                  | 11          | 20         | 5.5          | 10         |  |  |  |

| 12                                  | 12          | 24         | 6            | 12         |  |  |  |

| 13                                  | 13          | 28         | 6.5          | 14         |  |  |  |

| 14                                  | ≥14         | ≥32        | ≥7           | ≥16        |  |  |  |

### $YARR\_ToT = Chip\_ToT + 1$

Timon Heim

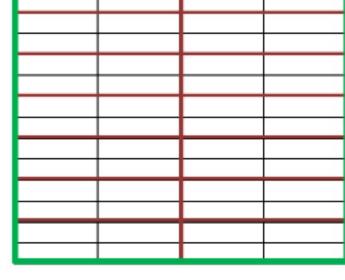

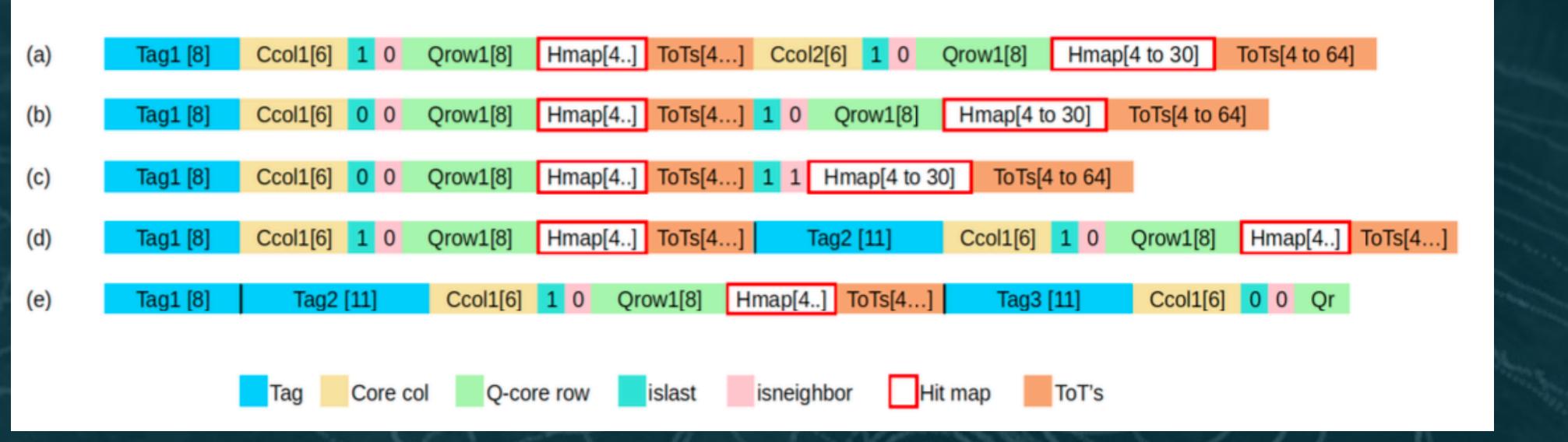

- Region Hit

- ToT latch

- ToT Code

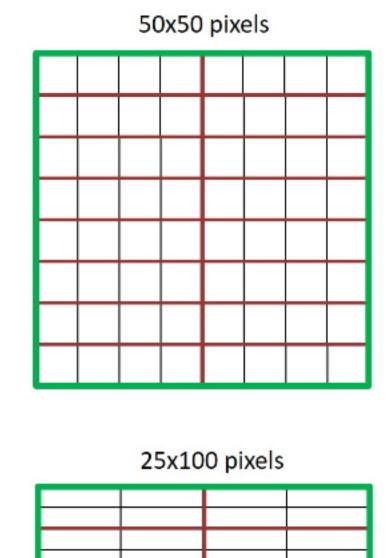

50x50 pixels

25x100 pixels

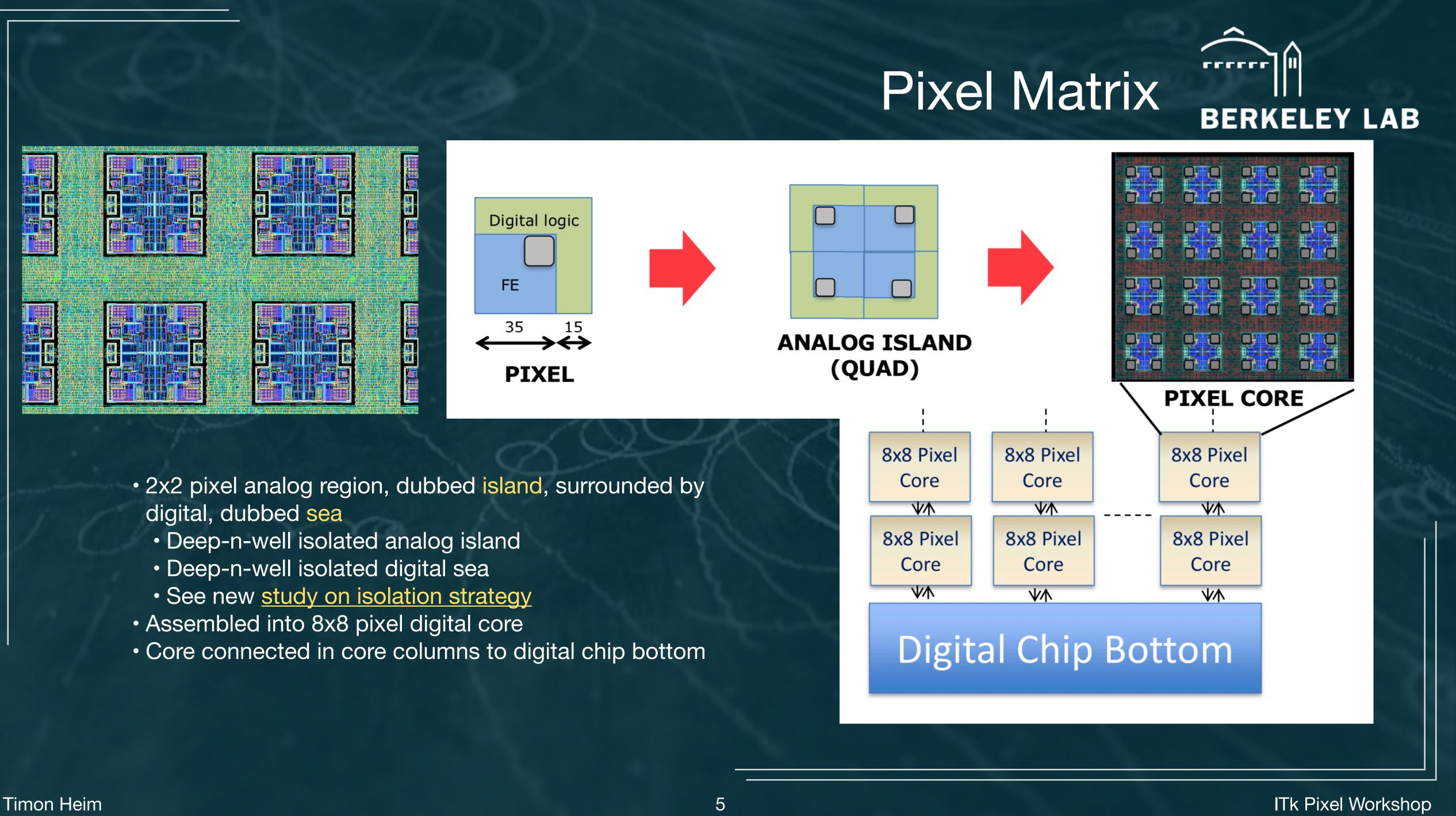

Pixel core: 8 x 8 = 64 pixels,  $2 \times 8 = 16$  pixel regions

### Timon Heim

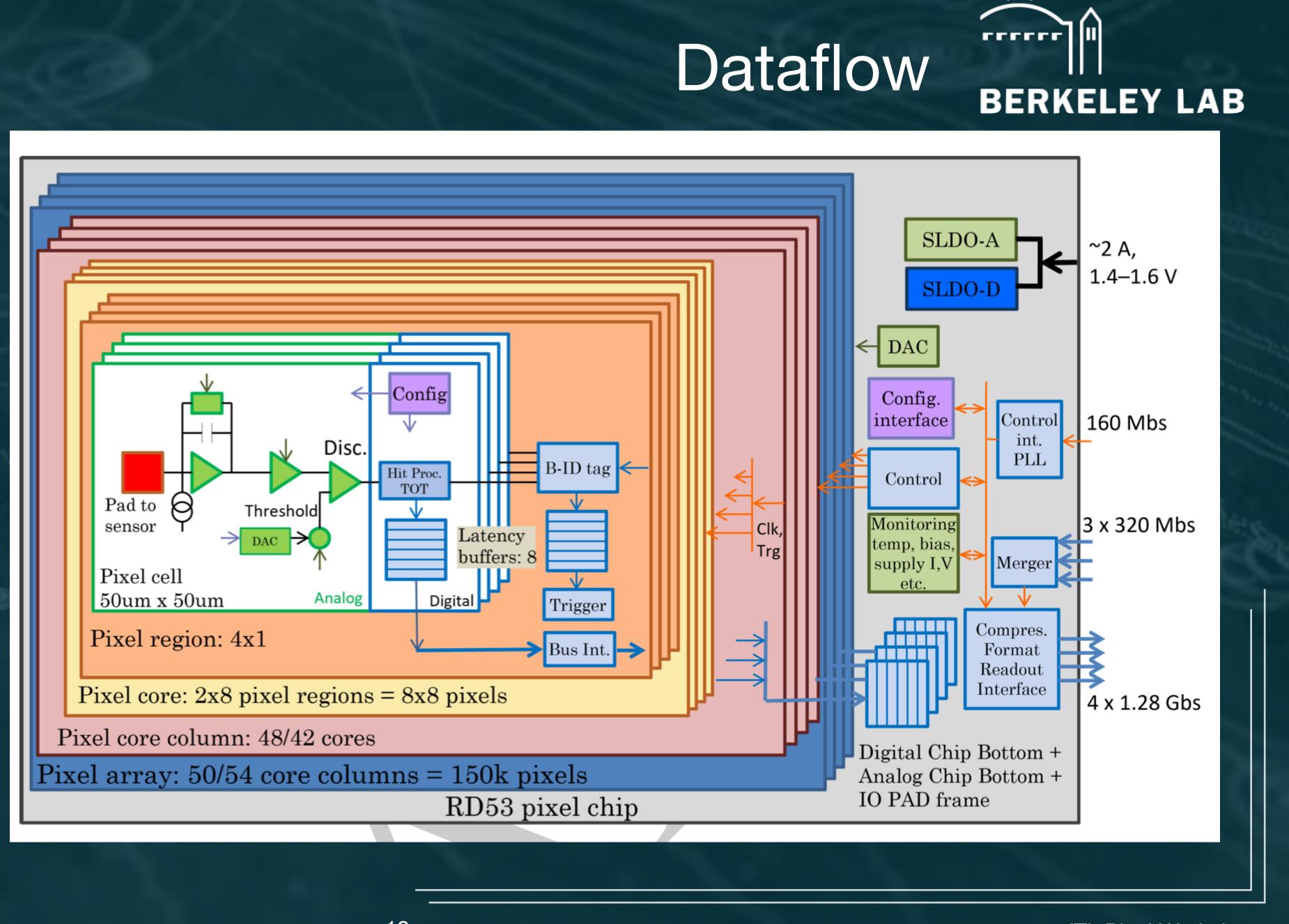

Trigger Delay: defined in scan config as part of trigger loop Latency: part of chip config

$$t_{hit} = t_{trig}$$

Timon Heim

gger - latency

Trigger Commands: 16bit frame stretches over 4 bunch crossings => 15 different trigger commands for all possible combinations

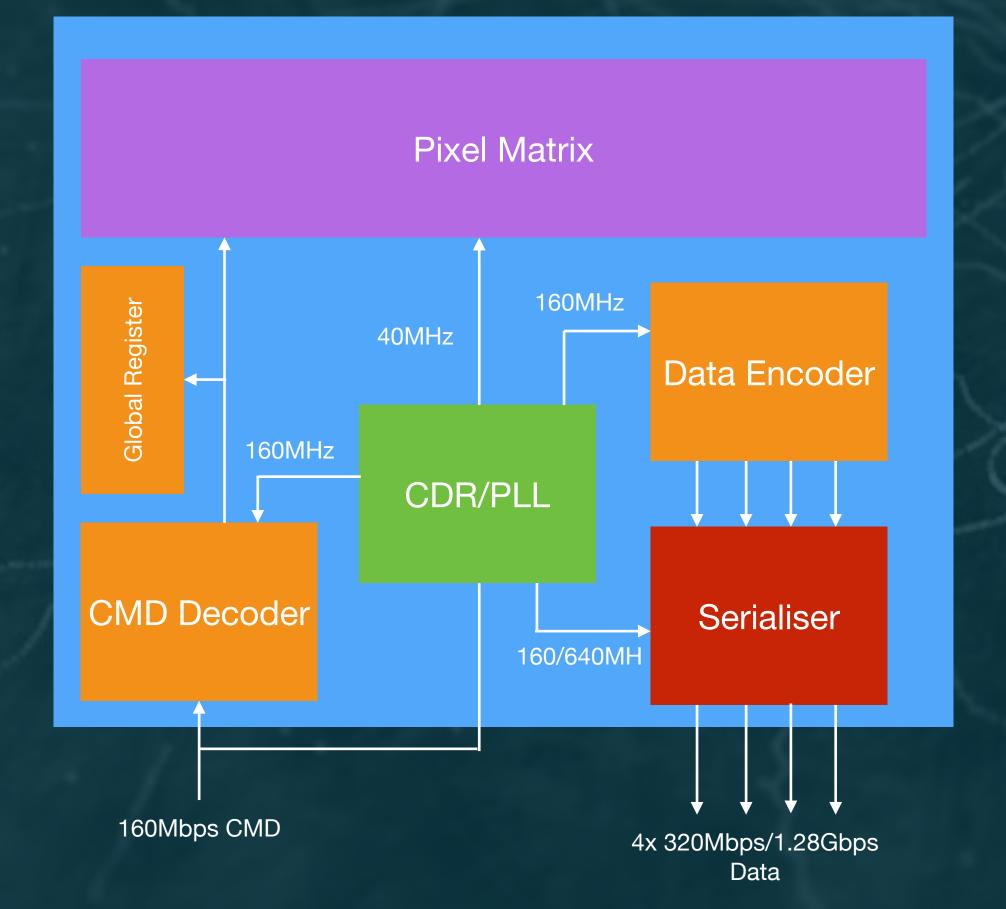

- Sending only single CMD signal to chip (custom DC balanced encoding) CDR/PLL recovers 160MHz clock and generates clocks for different domains (LHC runs with 40MHz bunch crossing frequency)

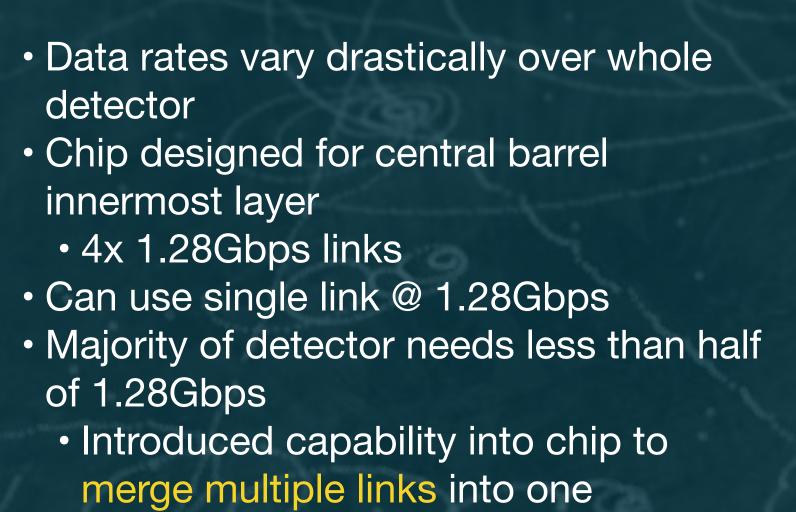

- High output speed requires 8x multiplication of recovered clock • Total of four 1.28Gbps output lanes which can be bonded into one Aurora 64b/66b channel (320Mbps in case of data merging)

## Digital I/O

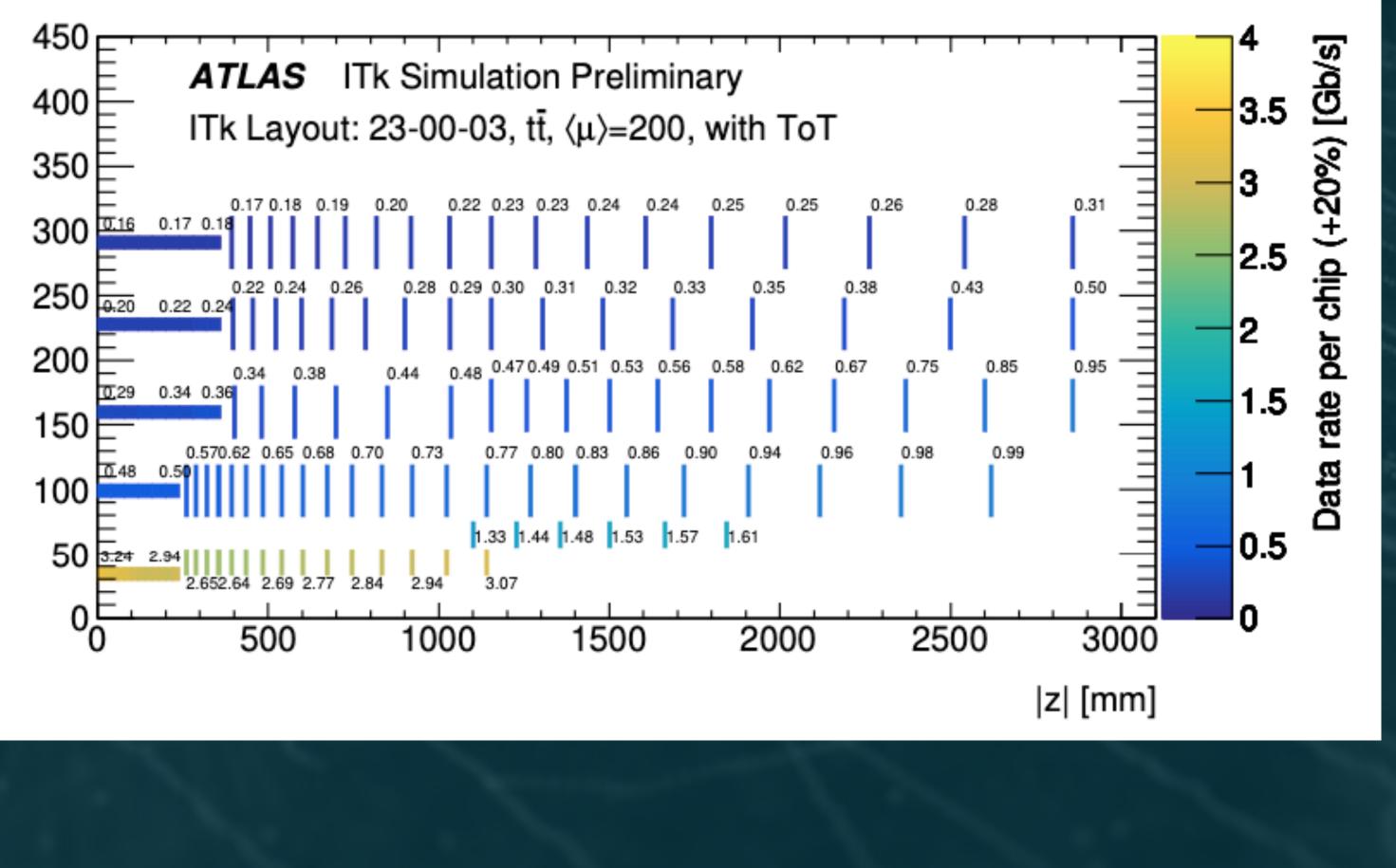

R [mm]

### Timon Heim

### Data Rates

### **Common Quad Module:**

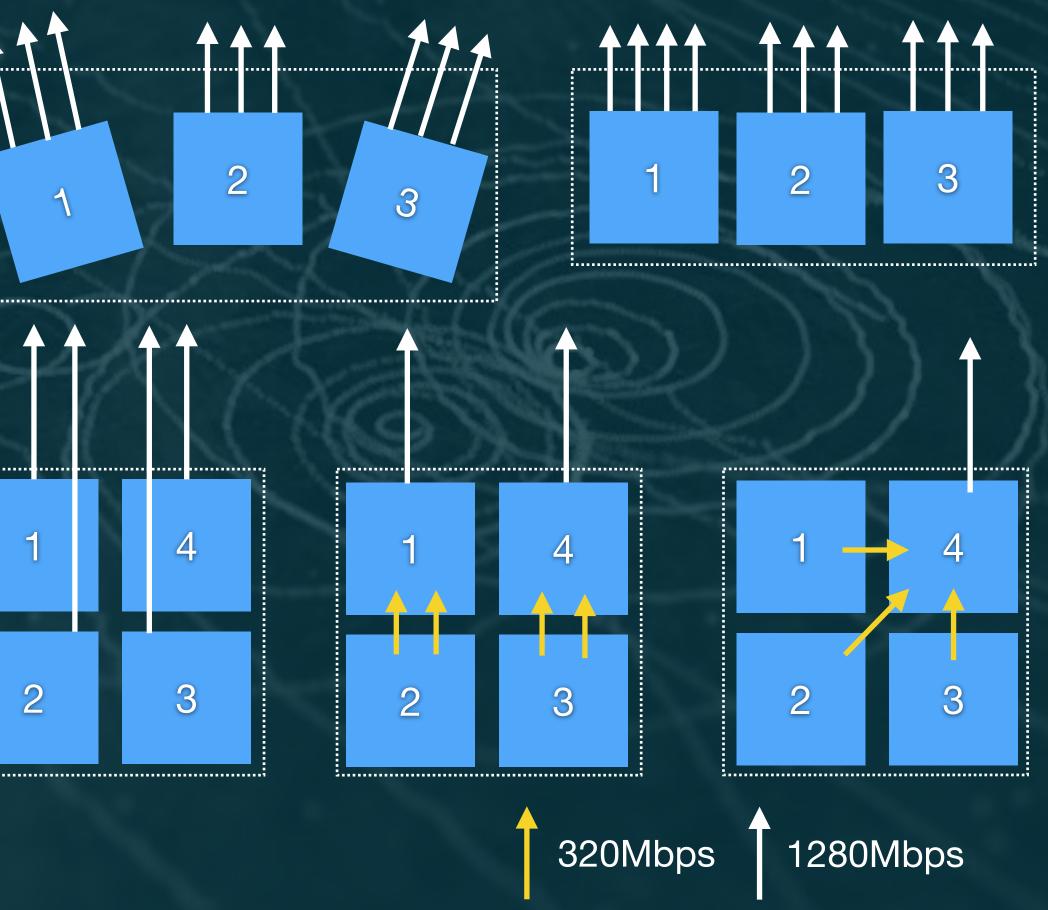

### Three possible modes, chosen via chip configuration

- 1 link per chip

- 0.5 links per chip (1 primary, 1 secondary)

- 0.25 links per chip (1primary, 3 secondary)

|         | Layer | Section              | Number of Links/FE  |     |

|---------|-------|----------------------|---------------------|-----|

| Triplet |       | Flat barrel          | 4                   |     |

|         | 0     | Barrel rings         | 3                   |     |

|         |       | End-cap rings        | 2                   |     |

|         | 1     | Flat barrel          | 0.5                 |     |

|         |       | Barrel rings         | 1                   |     |

|         |       | End-cap rings        | 1                   |     |

|         | 2     | Flat barrel          | 0.5                 |     |

|         |       | Barrel rings         | 0.5                 |     |

|         |       | End-cap rings (1-5)  | 0.5                 |     |

|         |       | End-cap rings (6-11) | 1                   |     |

|         | 3     | Flat barrel          | 0.25                |     |

|         |       | Barrel rings         | 0.25                |     |

|         |       | End-cap rings        | 0.5                 |     |

|         | 4     | Flat barrel          | 0.25                |     |

|         |       | Barrel rings         | 0.25                |     |

|         |       | End-cap rings (1-7)  | 0.25                |     |

|         |       |                      | End-cap rings (8-9) | 0.5 |

|         |       |                      |                     |     |

## Link Configuration

Triplet Module:

- Linear Triplet: 4 links per chip

- Ring Triplet: 3 links per chip

- Link layer protocol: Aurora 66b/66b:

- Only 3% overhead, DC balanced through scrambling, support of K-words for non-hit-data transfer (register reads)

- Custom data encoding (compression):

- Had to serve wide range data sparsity, from dense small cluster hits in the inner layer, to sparse large clusters in out layer

- Hit data organized in "streams", each stream can contain more than one event to effectively use 64bit aurora frame (though ATLAS choose not to use this feature)

- Streams are not-byte aligned, hit addresses can be relative to previous address

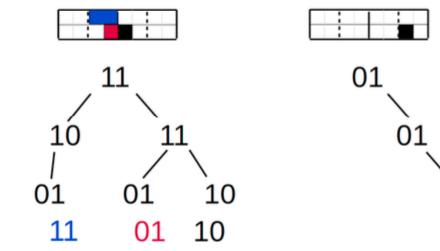

- Hit maps combine 4 1x4 pixel regions (16 pixel), hit maps are encoded as binary trees, length can vary

## Data Output Protocol

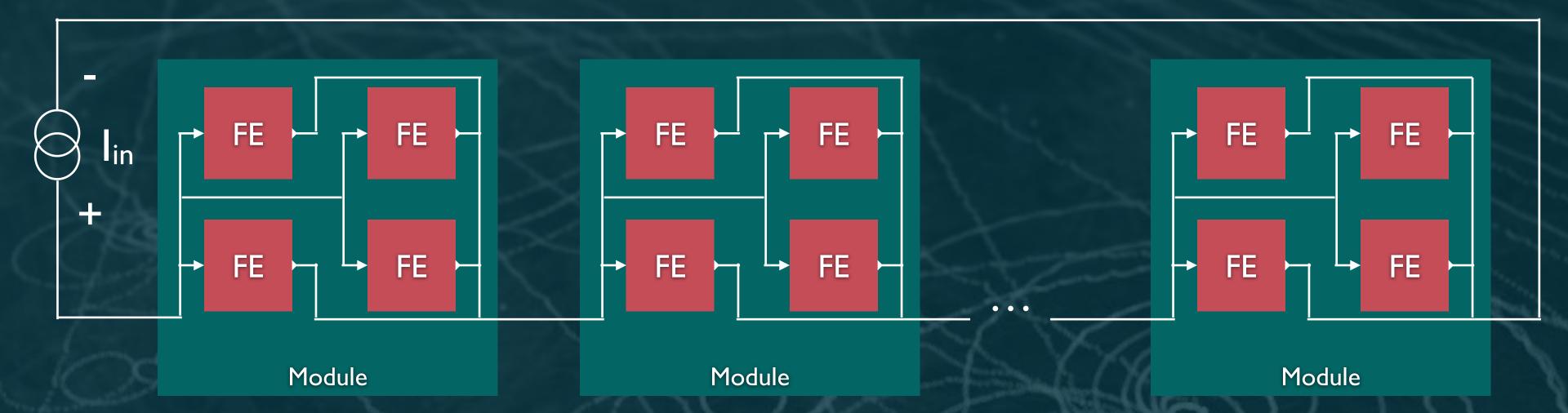

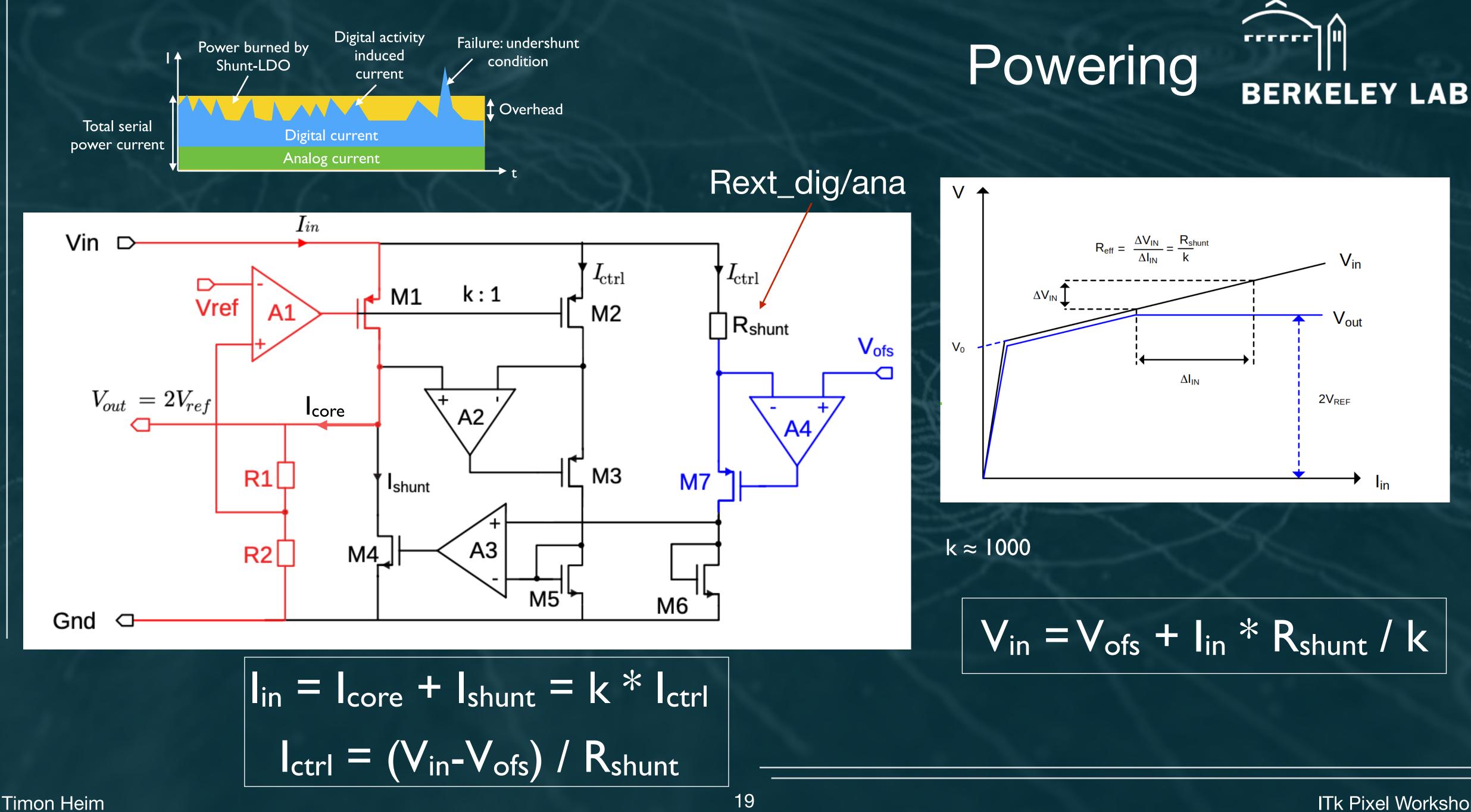

- Advantage of serial powering:

- Parallel powering: current scales with modules

- Serial powering: voltage scales with modules

- But serial powering requires module impedance to be constant

- If impedance is not constant over time, power supply will have to react

- PSU reaction is delayed due to cable inductance

- => Impedance changes result in voltage transients in chain

- Chip impedance inherently not constant but depends on activity

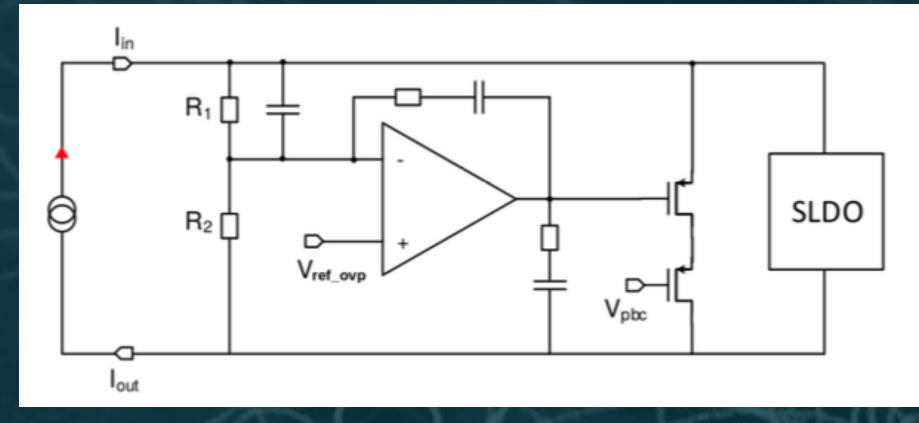

- Shunt LDO circuit stabilizes chip impedance to the outside world

## Serial Powering

• Power loss in cable:  $P_{heat} = R_{cable} * I^2 => Less current => Less mass (Higher resistance)$

|                                           |        |         |            | 4 |

|-------------------------------------------|--------|---------|------------|---|

|                                           |        |         |            |   |

|                                           | Analog | Digital | Total Chip | ľ |

| Analog Periphery [A]                      | 0.120  |         | - AL       |   |

| Analog Matrix [A]                         | 0.440  |         | 1200       |   |

| Digital Periphery [A]                     |        | 0.250   |            |   |

| Digital Periphery Activity [A]            |        | 0.010   |            |   |

| Digital Matrix [A]                        |        | 0.450   |            |   |

| Digital Matrix Activity [A]               |        | 0.040   | 1 1        | • |

| Icore[A]                                  | 0.560  | 0.750   | JAN (      |   |

| I <sub>core</sub> + overhead (10/20%) [A] | 0.616  | 0.900   | Ser.       |   |

| shunt                                     | 0.056  | 0.150   | . 1        | • |

| l <sub>in</sub> current per chip [A]      |        | A.      | 1.516      |   |

| k                                         | 1000   | 1000    |            |   |

| Offset [V]                                |        | 5       | 1.000      |   |

| Target V <sub>in</sub> [V]                |        | 2       | 1.500      |   |

| R <sub>ext</sub> [Ohm]                    | 812    | 556     |            |   |

| R <sub>eff</sub> [Ohm]                    |        |         | 330        |   |

## An Example

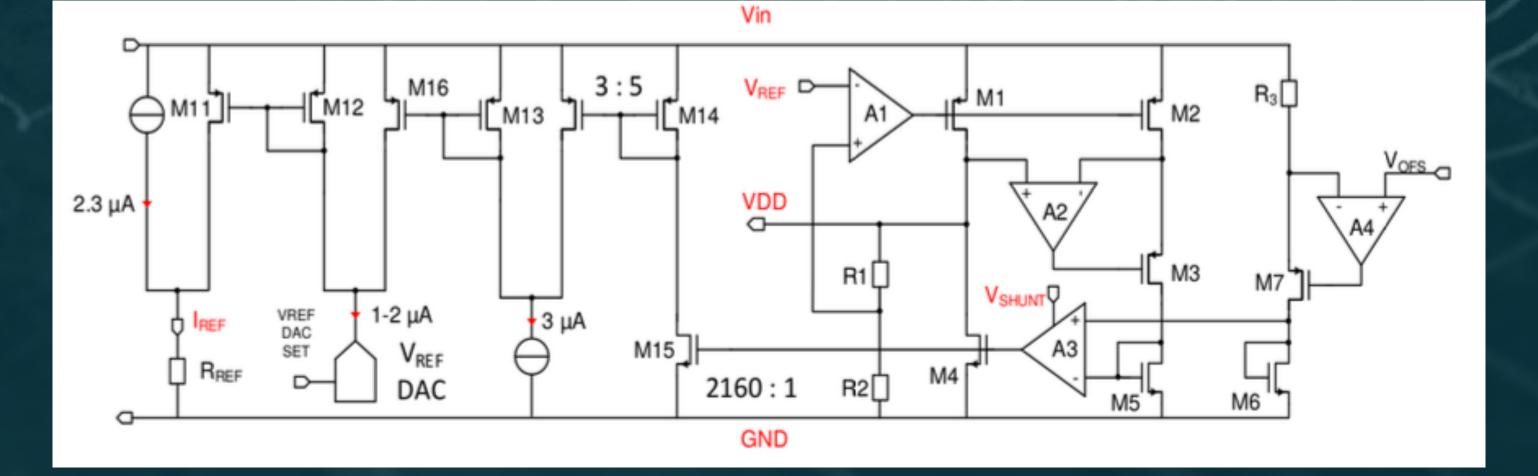

### $R_{shunt} = (V_{in} V_{ofs}) / I_{ctrl}$ $= (V_{in} V_{ofs}) / (I_{in} / k)$ $V_{in} = V_{ofs} + (R_{eff} * I_{in})$

Impedance of chip/module will be equal to R<sub>eff</sub> unless I<sub>shunt</sub> goes to 0A!

6.064

Total Module

ITk Pixel Workshop

82

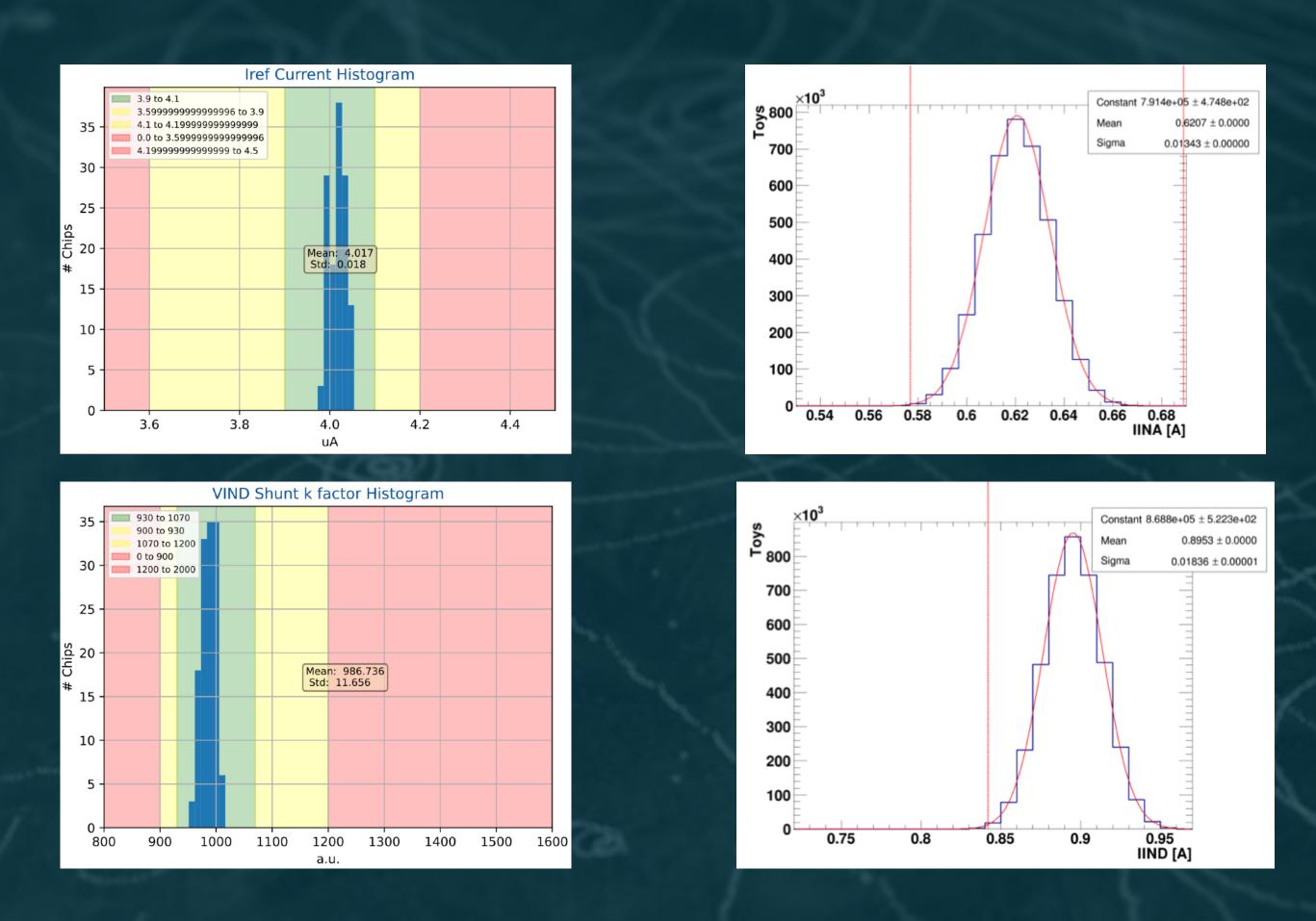

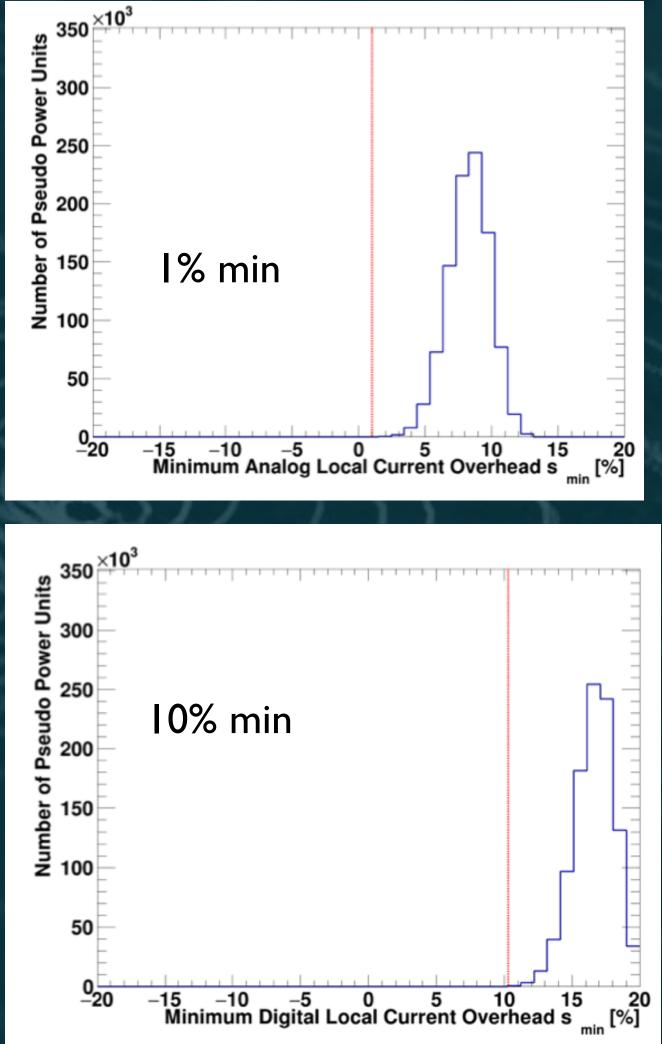

- Variations in k-factor, resistance, Vin, and Vofs will lead to change in impedance

- k-factor measured on cut on during wafer probing

- 0.1% tolerance resistors

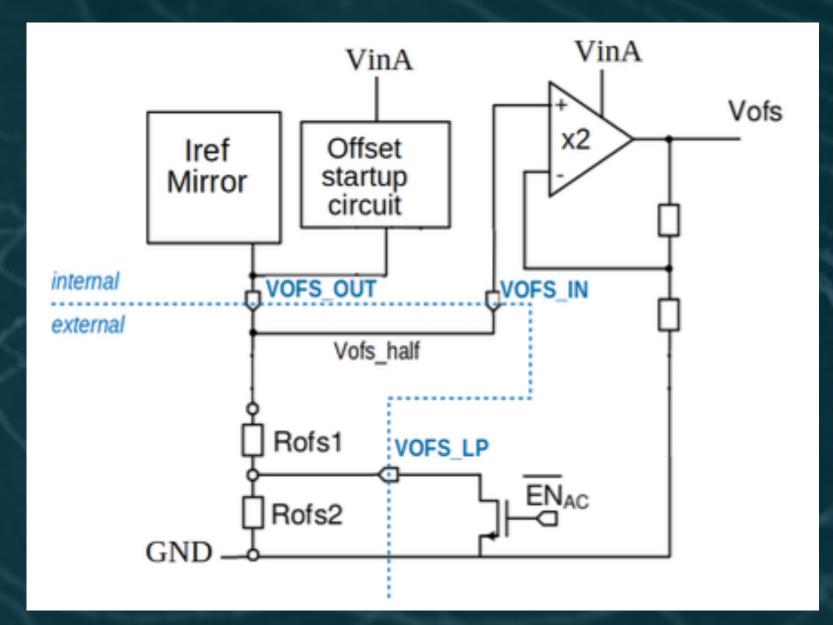

- $V_{ofs} = 2^*(R_{ofs}^*I_{ref}) => Ref$  measured and cut on during wafer probing

- Variation in impedance will lead to unequal current splitting in module

- Lower impedance chips will take away current from higher impedance chips

- Variation in Icore will lead to reduced overhead

## The Culprit

# Backup

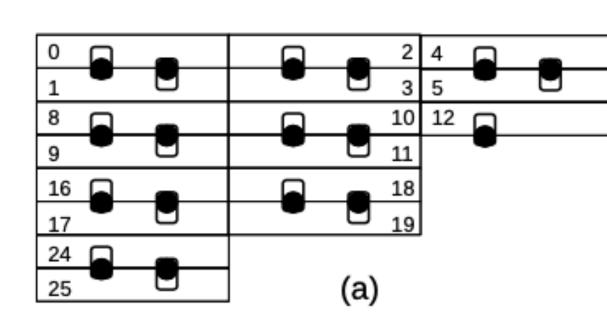

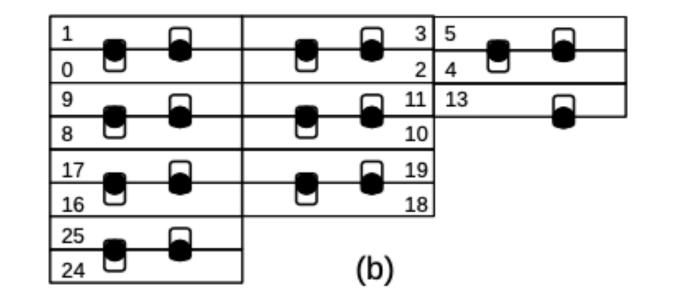

Figure 48: Two options (a and b) for mapping of  $25 \,\mu m \times 100 \,\mu m$  pixel sensors to the core pixel address. Which option is correct is determined by the sensor metalization. The filled circles represent the bump bond locations while the open rounded rectangles extend from each bump to the center line of the sensor pixel served. The top left corner of an 8 by 8 pixel core is shown.

Timon Heim

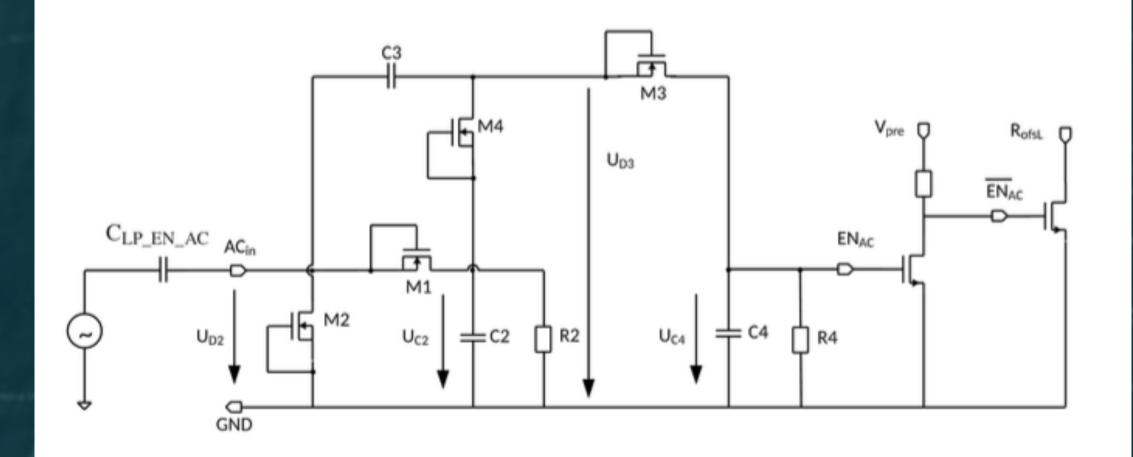

### Low Power Mode

### Overvoltage ···· & Undershunt Protection **BERKELEY LAB**

ITk Pixel Workshop

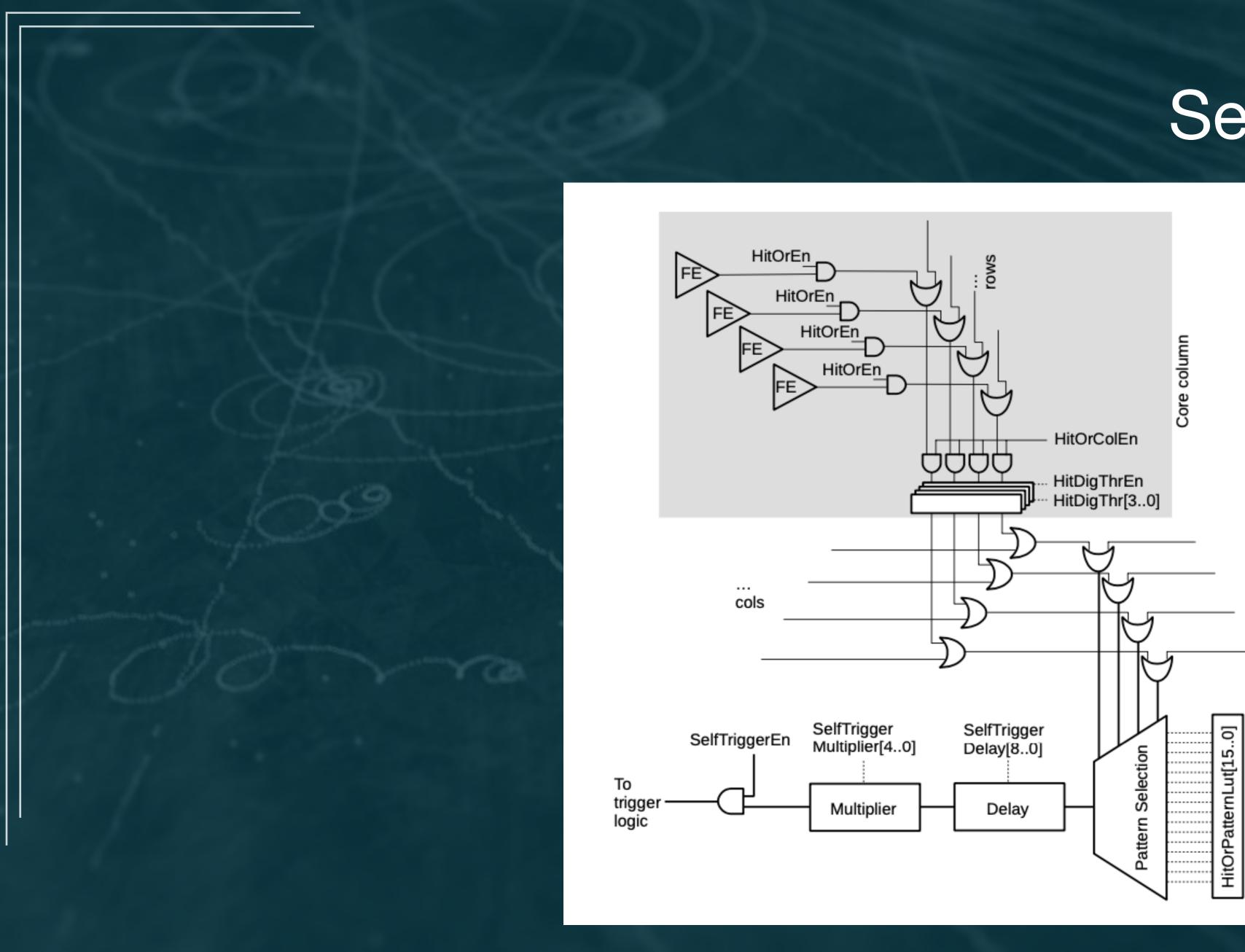

## Selftrigger

ITk Pixel Workshop

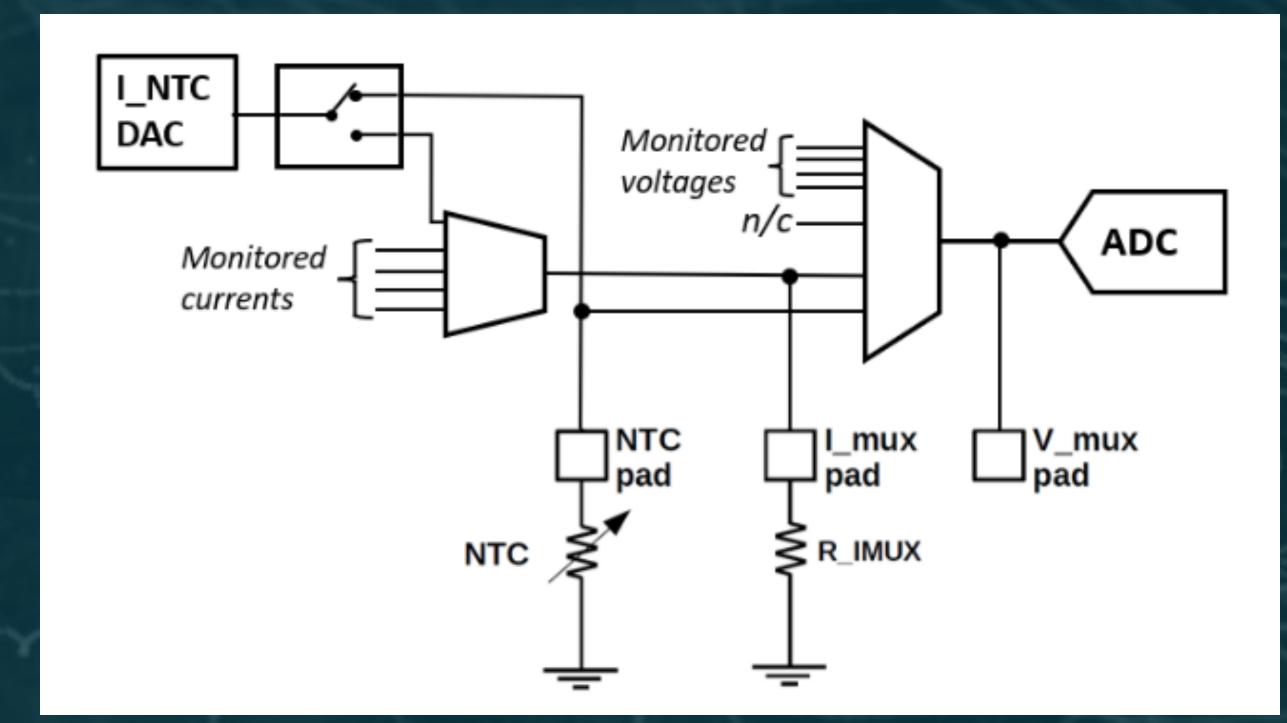

## Vmux/Imux