# Future directions and challenges of ASICs

M. Garcia-Sciveres Lawrence Berkeley National Lab

2023 HSTD13 - Vancouver

# Silicon Detectors at Colliders

BERKELEY LAB

(and in orbit)

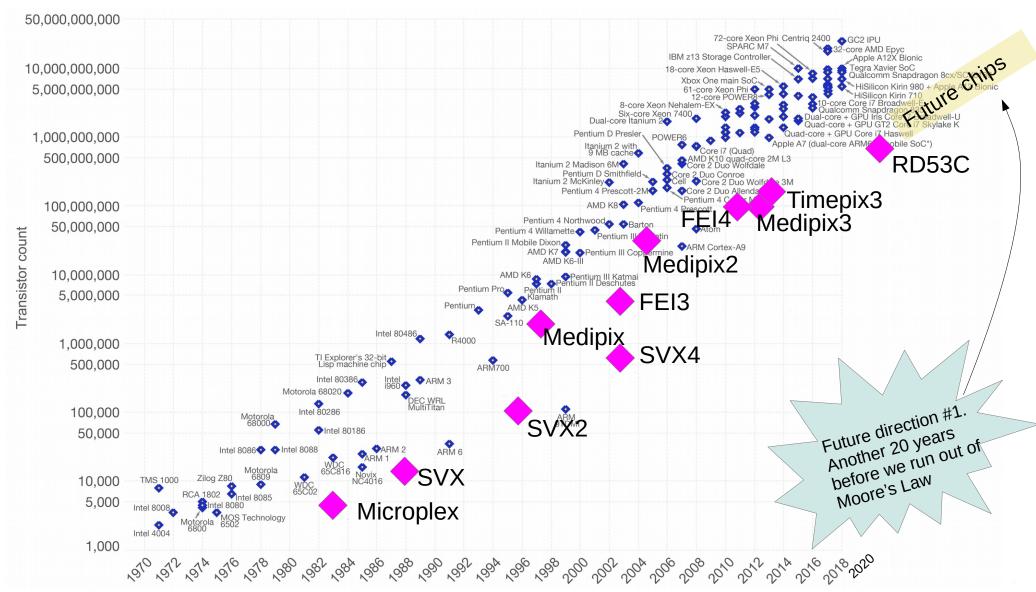

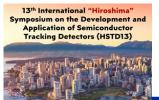

# Tracker ICs vs Microprocessors

# Aside: This Just Out:

### Microelectronics in High Energy Physics

#### Edited by

- Alessandro Marchioro Experimental Physics,CERN,Switzerland

- Philippe Farthouat Experimental Physics, CERN, Switzerland Last update 21 August 2023

## **Aside: Contents**

Contents lists available at ScienceDirect

#### Nuclear Inst. and Methods in Physics Research, A

journal homepage: www.elsevier.com/locate/nima

Particle physics experiments: From photography to integrated circuits

Erik H.M. Heijne

IEAP/CTU, Husova 240/5, CZ 110 00 Prague 1, Czech Republic CERN EP Dept, 1 Esplanade des Particules, CH 1211 Geneva 23, Switzerland Nikhef, Science Park 105, 1098XG Amsterdam, Netherlands

#### Front-end electronics for silicon strip trackers: Architectures and evolution

#### Jan Kaplon

CERN, 1211 Geneva 23, Switzerland

#### Hybrid pixel readout integrated circuits

#### Maurice Garcia-Sciveres

Lawrence Berkeley National Laboratory, Berkeley, USA

# Monolithic CMOS Sensors for high energy physics — Challenges and perspectives

W. Snoeys

CERN, Esplanade des Particules, CH-1211 Geneva 23, Switzerland

# ASIC survival in the radiation environment of the LHC experiments: 30 years of struggle and still tantalizing

#### Federico Faccio

CERN, EP department, Esplanade des Particules 1, Meyrin, 1211, Switzerland

#### Radiation tolerant optoelectronics for high energy physics

Jan Troska a,\*, François Vasey a, Anthony Weidberg b

#### ASICs for LHC intermediate tracking detectors

G. Hall a,\*, A.A. Grillo b

a Blackett Laboratory, Imperial College, London SW7 2AZ, UK

#### Cryogenic electronics for noble liquid neutrino detectors

Hucheng Chen\*, Veljko Radeka

Brookhaven National Laboratory, Upton, NY, United States of America

Analog-to-digital converters and time-to-digital converters for high-energy physics experiments

Ping Gui

Southern Methodist University, Dallas, TX, USA

Radiation-hard ASICs for data transmission and clock distribution in High Energy Physics

Paulo Moreira\*, Szymon Kulis

CERN, European Center for Nuclear Research, Switzerland

<sup>&</sup>lt;sup>a</sup> EP Department, CERN, Esplanade des Particules, Geneva, 1211, Switzerland

<sup>&</sup>lt;sup>b</sup> Physics Department, Oxford University, Denys Wilkinson Building, Oxford, OX1 3RH, United Kingdom

<sup>&</sup>lt;sup>b</sup> Santa Cruz Institute for Particle Physics, University of California, Santa Cruz, CA 95064, USA

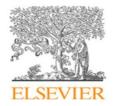

# Why Microplex?

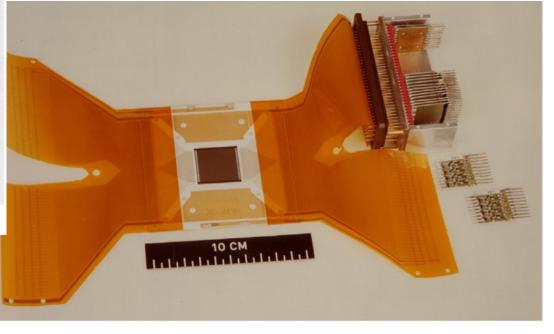

Because these were silicon strip modules before:

#### NA11, CERN 1981

NIM205 (1983) 99

### They did not scale

Fig. 13. Microstrip detector and the MSD2 4-channel hybrid readout circuits, providing high density signal processing in a relatively small volume (CERN photo-8310560).

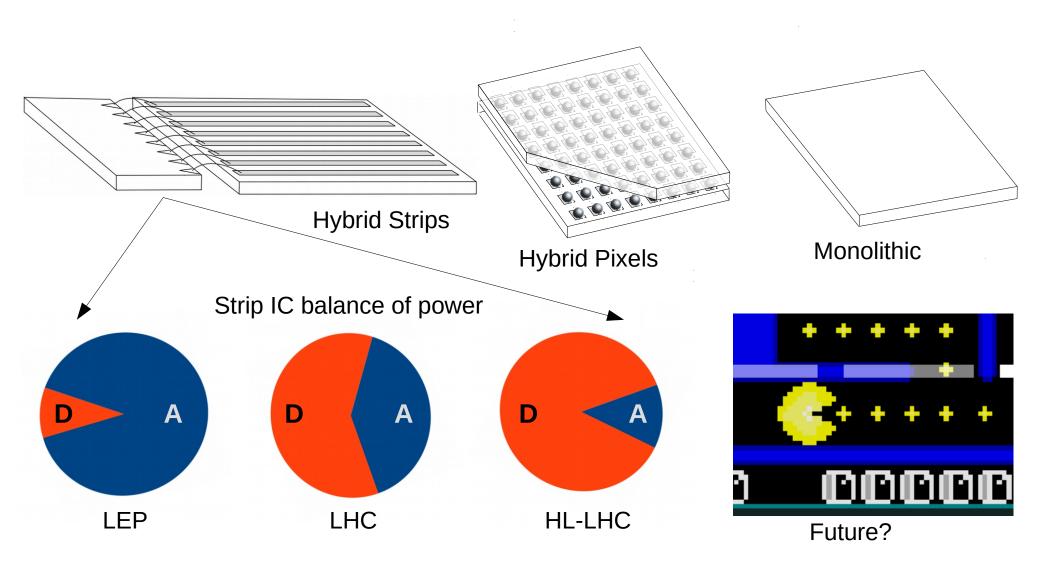

# Silicon Tracker Types

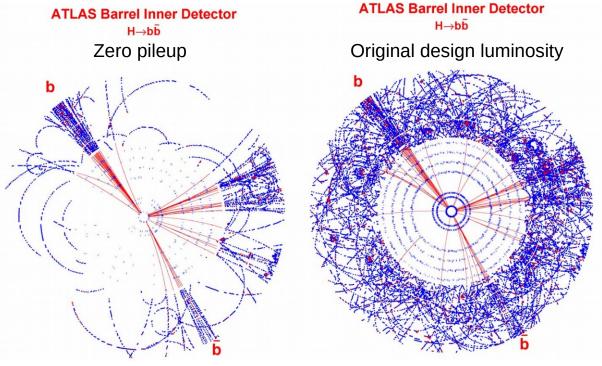

# **Hybrid Pixel Readout**

#### Original ATLAS motivation for pixels circa 1995

#### HL-LHC is far beyond

FE-I3 readout chip

Solution:

16 chips. 46,080 bump bonds

Xray of bumps

6.3cm

It did not scale.

A new readout chip solution had to be developed

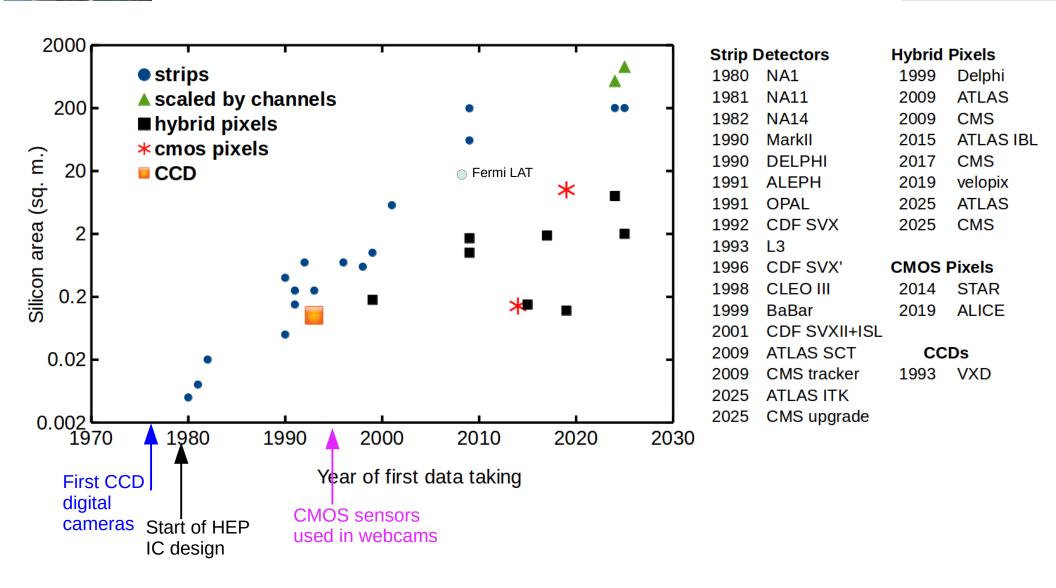

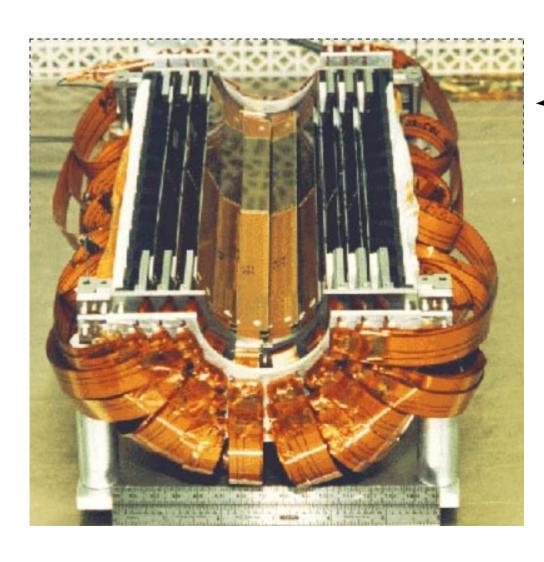

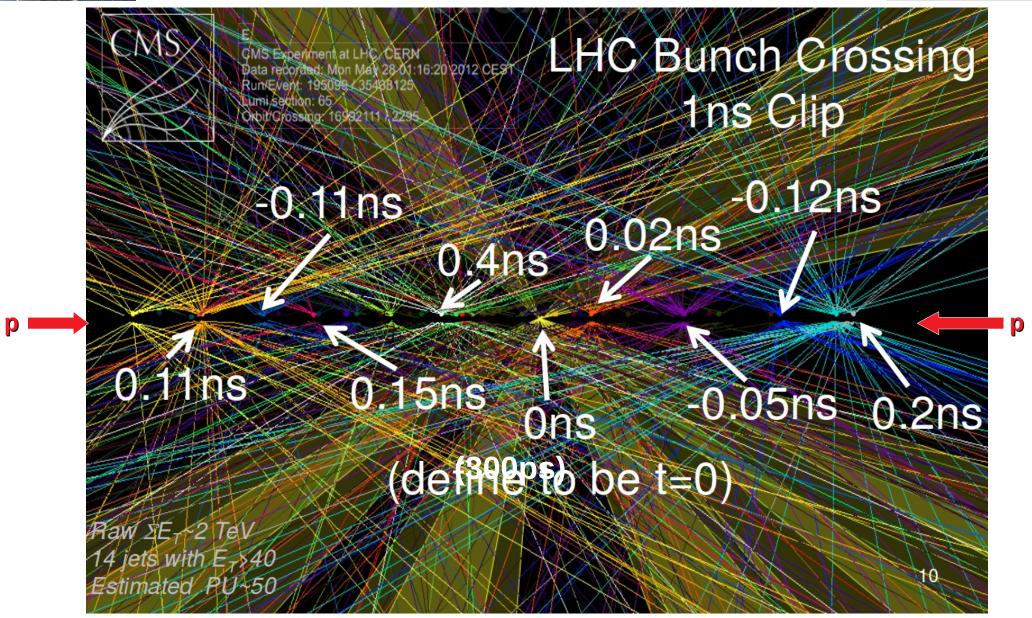

### The Rate Extremes

- Silicon area: 0.12 m²

- 300M pixels (20μm x 20μm)

- But only 350,000 Z decays recorded

strips

scaled by channels

hybrid pixels

cmos pixels

=> most pixels were never hit by real collision particle!

#### **HL-LHC**

Inner layers of ATLAS and CMS high luminosity upgrades will see 10 collision particles in every Si atom!

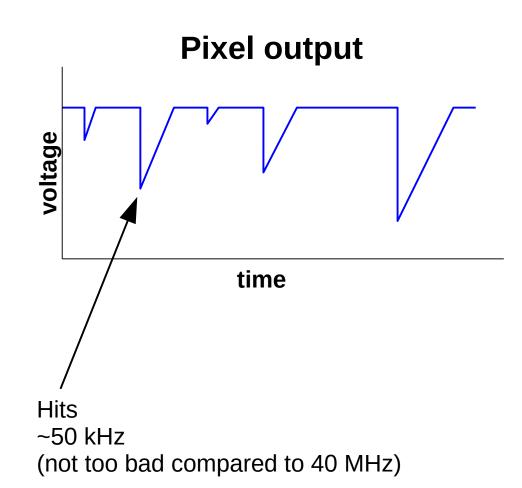

# Single Pixel Perspective

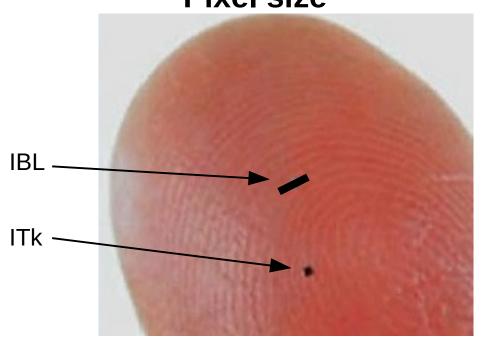

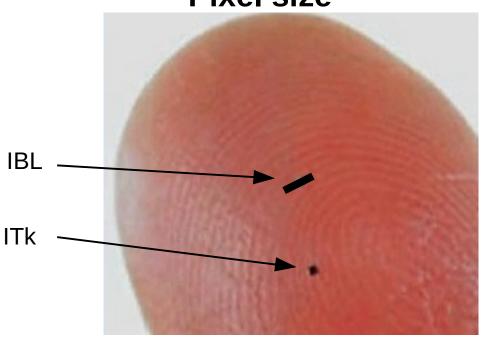

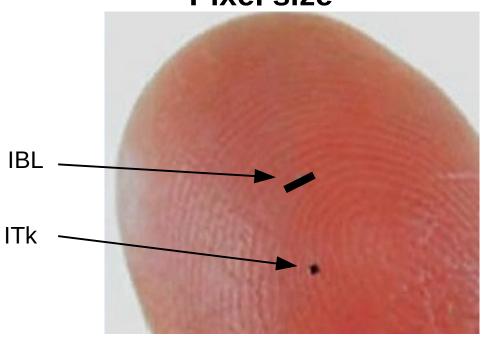

#### **Pixel size**

# Single Pixel Perspective

# Single Pixel Perspective

#### **Pixel size**

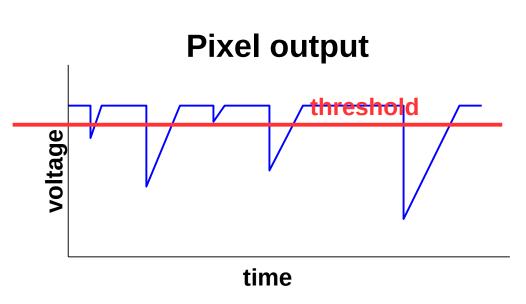

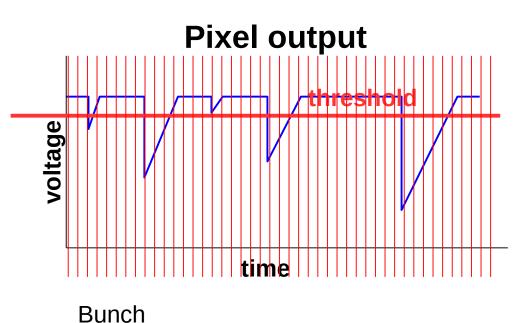

Digitize amplitude above threshold in each Bunch Crossing

crossings

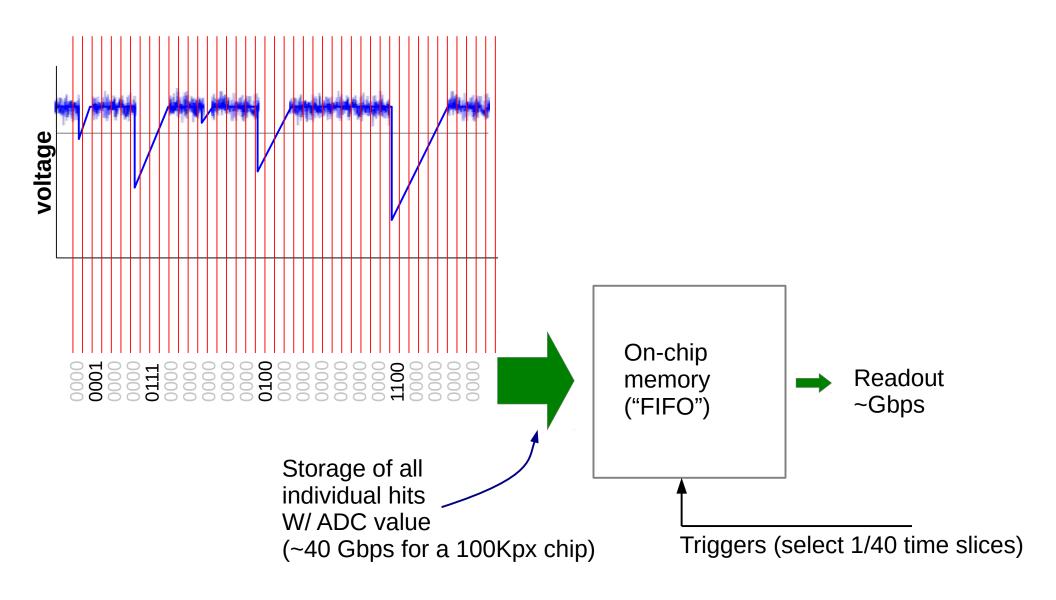

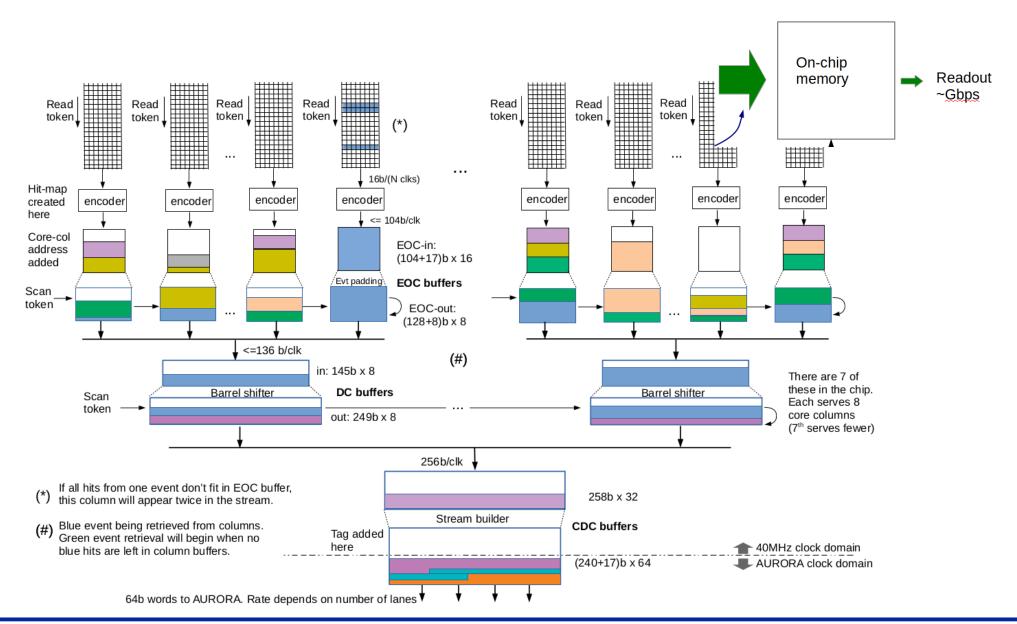

# On-Chip Storage and Trigger

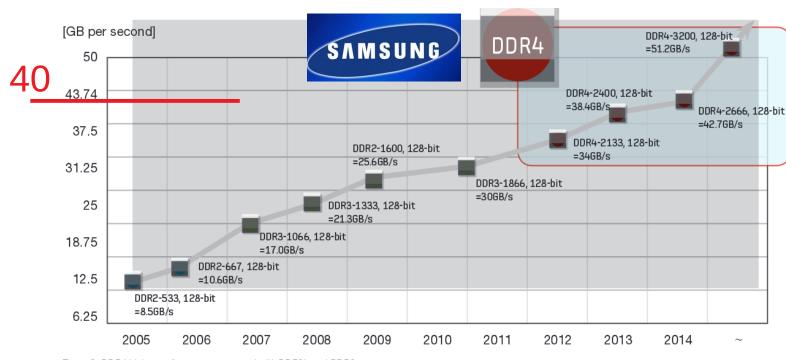

# Storing data at 40Gbps

High rate pixel readout chips are memories (in addition to being pixel readout chips)

Plot is for a memory module containing 8 silicon chips so B = b

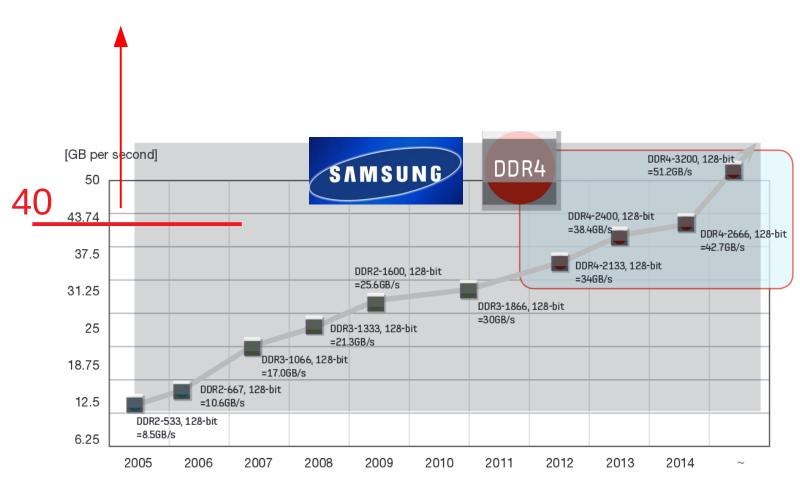

Figure 2. DDR4 higher performance compared with DDR3L and DDR2

(and this is not rad hard)

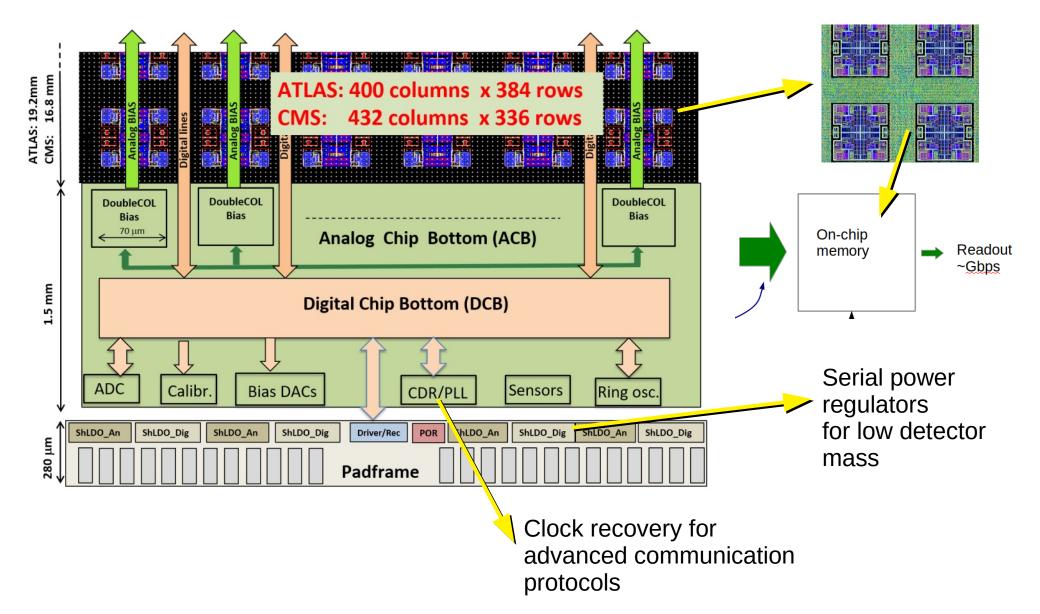

# RD53 Hybrid Pixel Readout for higher rate and radiation

Cern.ch/rd53

### **RD-53 Collaboration Home**

RD-53 will design and produce the next generation of readout chips for the ATLAS and CMS pixel detector upgrades at the HL-LHC. More details can be found in the 2018 extension proposal and the original collaboration proposal.

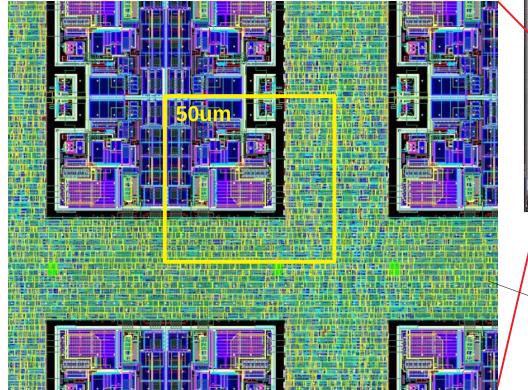

~1000 transistors

### Complex system on chip

### SOC trends will continue

- The more functionality the FE chip can take over the better

- Electrical communication, power distribution, environmental monitoring...

- Optical communication could be integrated in FE chip as CMOS foundries offer photonic options.

- But many system/assembly challenges and advantage not obvious

- Wireless functionality could be included on chip

- Significant R&D on wireless readout

- Not s much on wireless command and control, which has a very clear use case (have to see interplay with fast timing)

- FPGA and/or AI/ML functions now straightforward to include, but use cases must be developed.

- SEU tolerance is a big challenge for on-chip functionality

# What's the next scaling problem?

# Future direction #2 is timing

### That's a lot more data to store!

### >100

Figure 2. DDR4 higher performance compared with DDR3L and DDR2

### That's a lot more data to store!

This is already full in 65nm CMOS. But we still have 20 years of Moore's Law, So 28nm.

Turns out that 28nm not a bad choice also for this part either Needs to be fast with <50ps jitter And needs a TDS with <50ps resolution

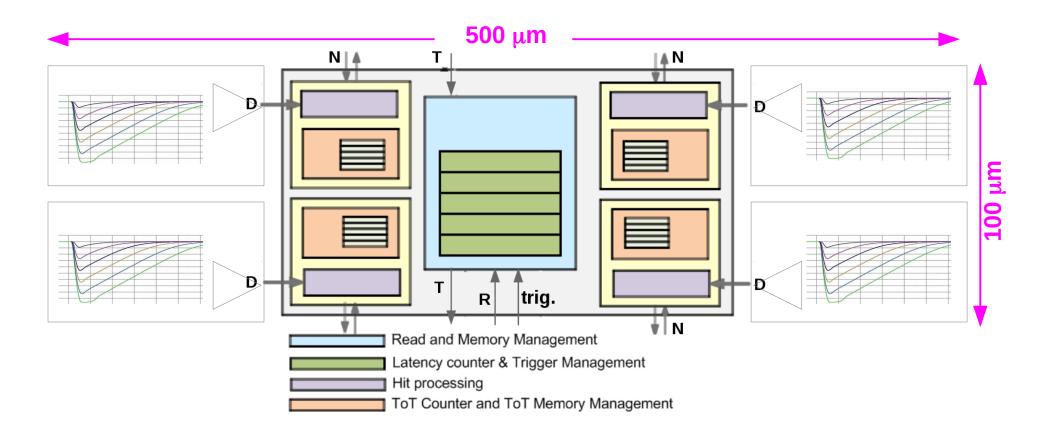

# Multiple efforts to design pixels with fast timing in 28nm

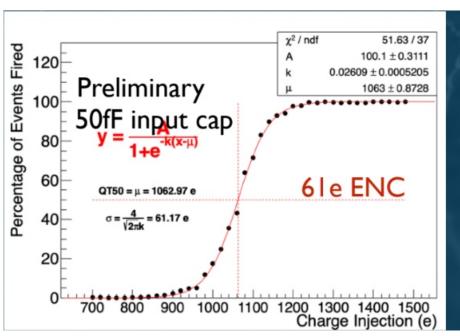

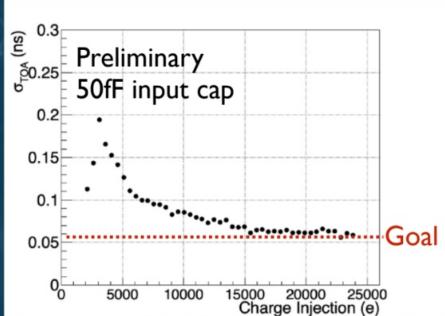

10u x30u FE, 4uW, <100e noise, ~50ps timing @ 50fF detector Cap

Next prototype already in fabrication adds:

Pixel TDC with 15u x15u , 1-2uW average power, using only 40MHz clock

### Data compression and C,D transmission

- Much larger data volume due to fast timing will require significant development

- How early can data be compressed?

- ML within the pixel matrix?

- Learned compression depending on chip location in detector?

- Advanced data transmission for x10 higher bandwidth with same power

- What about clock distribution and synchronization for fast timing?

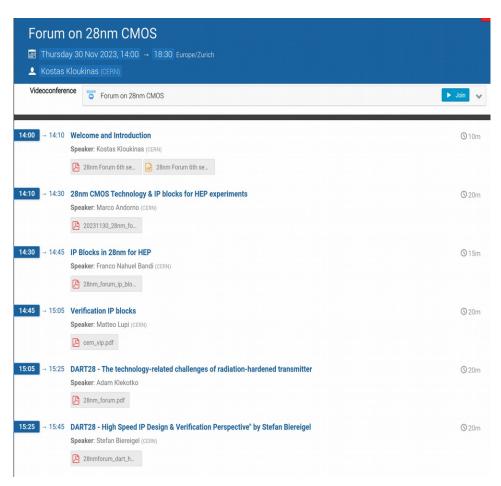

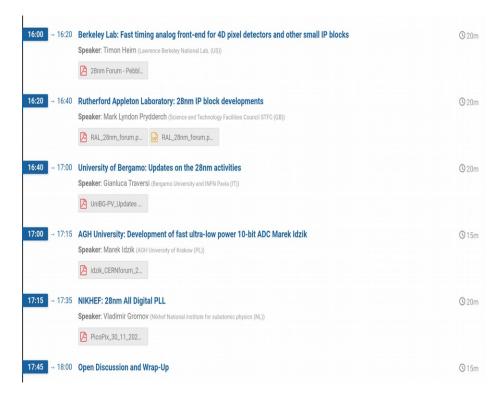

### 28nm Forum

Very different situation than 10 years ago when there was competition between: 130nm possibly with 3D stacking, 90nm and 65nm for the next generation of chips.

Today everyone is immediately on board with 28nm.

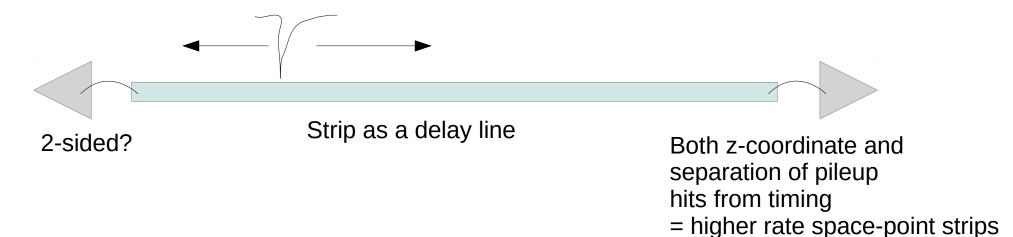

# What about Strips?

- Silicon strips are still 5-10X lower power and cost than hybrid pixels

- Good solution for very large area (not covering trade-offs with MAPS)

- So what about fast timing in strips?

- HL-LHC new LGAD-based timing detectors have channel capacitance comparable to strips

- => could make LGAD strips and fast timing strips readout chips

- And maybe that opens up new possibilities...

### Challenge: Modern chip design needs large effort

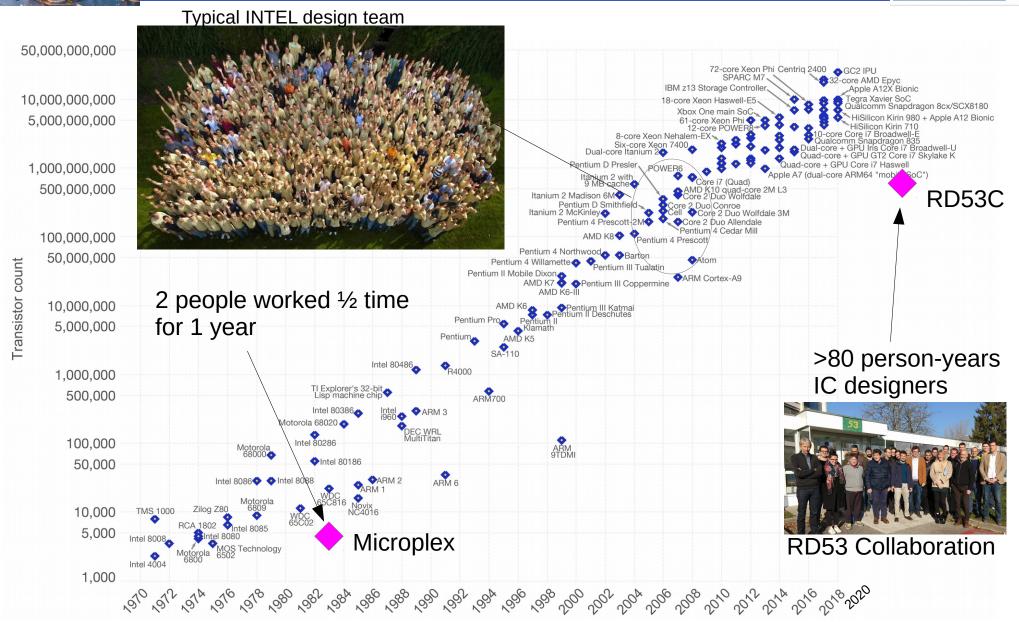

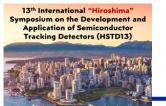

# Tracker IC Radiation Challenges

Inner Layer Dose

Temperature history Process details Dose rate Dose history Annealing

• • •

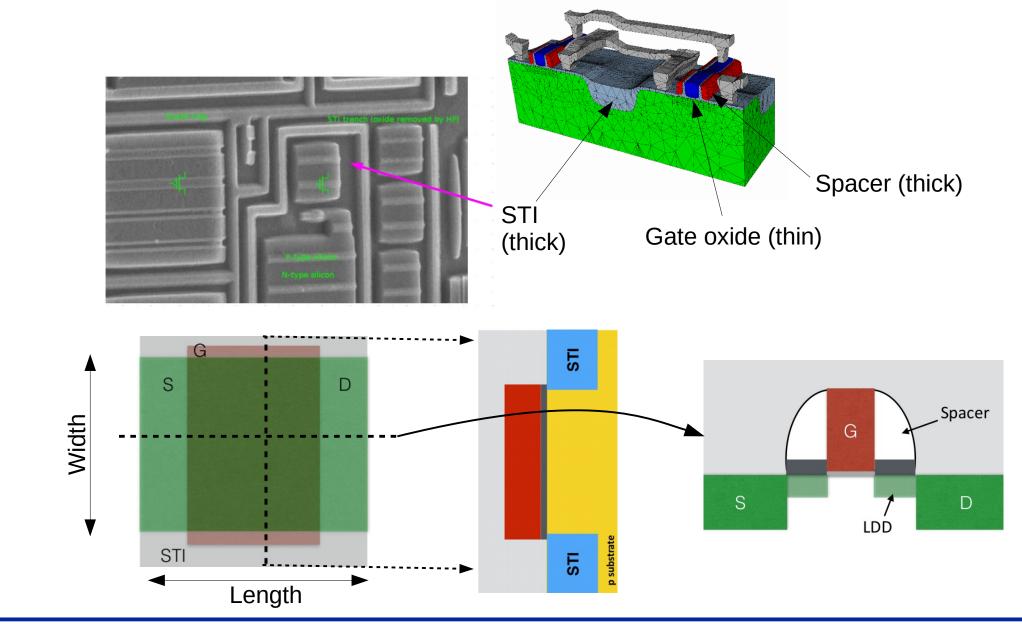

# STI, Gate, Spacer

# BACKUP

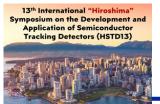

# Detector can image itself in 3D

## Example of non-trivial processing

# Limited Readout Bandwidth

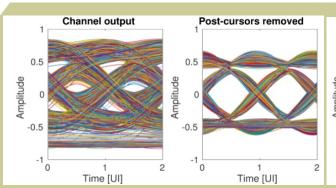

3m

**5Gbps Simulation**

5m

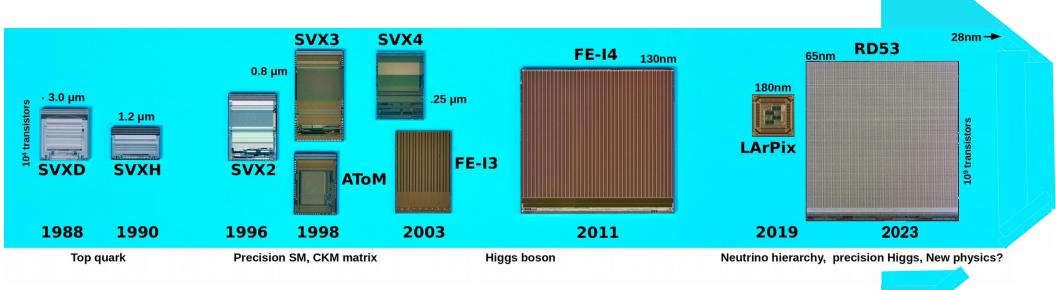

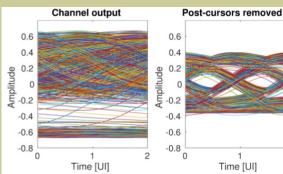

# Readout Chip Evolution

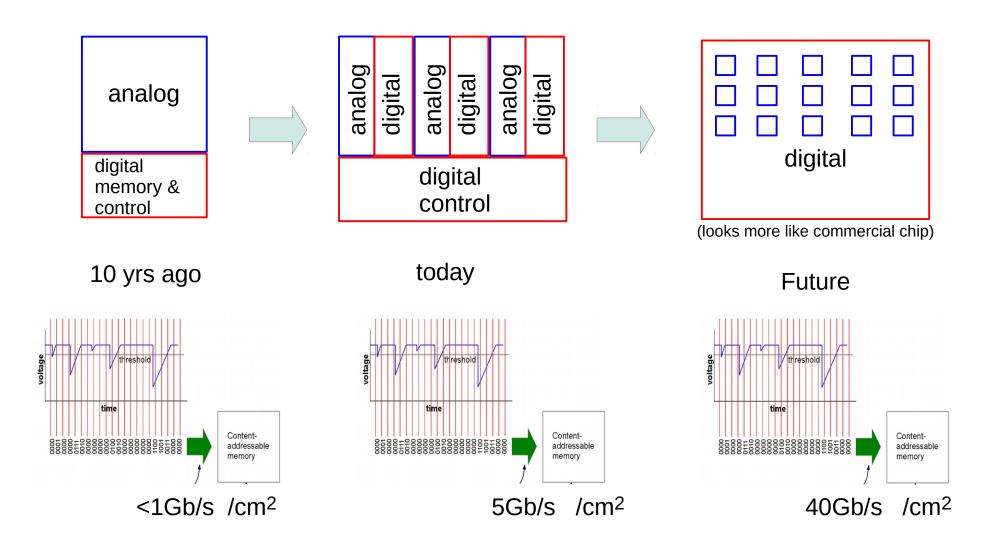

# Rad Hard Logic Density Scaling

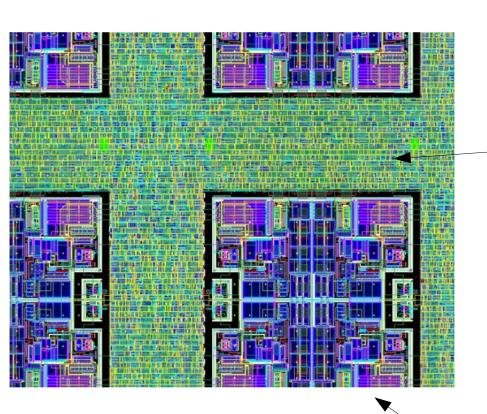

# FE-I4 Digital Region

Digital block is shared with 4 inputs- each form an identical analog pixel.

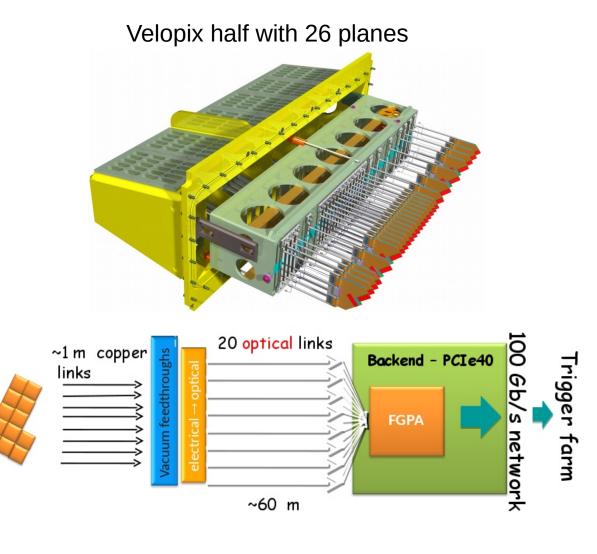

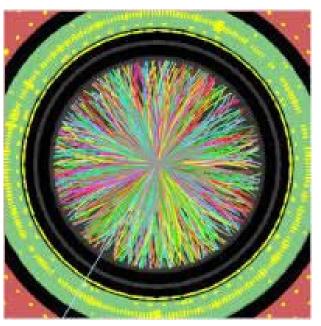

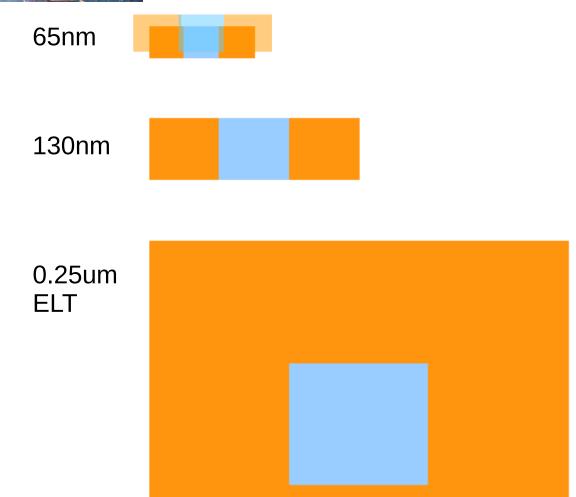

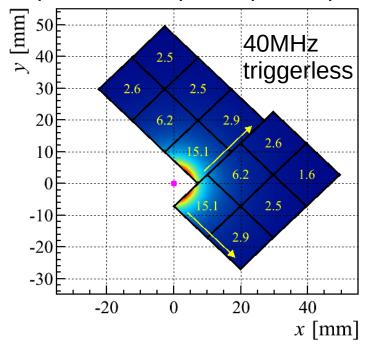

# Velopix triggerless readout

#### Readout chips in LHCb Velopix plane Output data rate per chip in Gbps

- Geometry looks like data flow diagram

- Lots of room outside physics acceptance

- Can have many cables out of each chip