# Pixel ASIC development for ATLAS and CMS

Maurice Garcia-Sciveres, Timon Heim, Maria Mironova

#### **ATLAS** Inner Tracker Upgrate

- All-silicon upgraded tracking detector (ITk) for HL-LHC to cope with increased instantaneous luminosity and pile-up

- Upgraded pixel detector:

- Larger silicon area  $\rightarrow$  6x larger than current tracking detector

- ~13 m2 of active area

- 9400 pixel modules

- 5.1 billion pixels

- Extended  $\eta$  coverage to  $|\eta| \le 4$

- Smaller pixel pitch:  $400 \times 50 \ \mu m^2 \rightarrow 50 \times 50 \ \mu m^2$

- New readout chip to cope with higher data rates and increased radiation

RD53A

ITk Pixel Module

Silicon Sensor

Bump bonds

Wirebonds

- Pixel chips for ATLAS and CMS upgrades have been jointly developed by the RD53 collaboration

- First joint prototype was RD53A, submitted in August 2017

- Half-sized demonstrator chip with three different analog front-end architectures (linear, differential and synchronous)

RD53A chip submission (Nov 2017)

### Digital Logic & Radiation tolerance

- Radiation tolerance requirement for HL-LHC: I Grad

- Digital logic gates particularly susceptible to radiation

- Chip includes ring oscillators for radiation testing > maximum allowed gate delay increase after I Grad is Digital gate delay increase with

\* Dose adjusted for copper layers

- Smallest transistors (strength 0) found to fail this requirement

- → Not used in the fina

- Additionally, dose rate affects damage

- → Factor 2 more damage at low dose

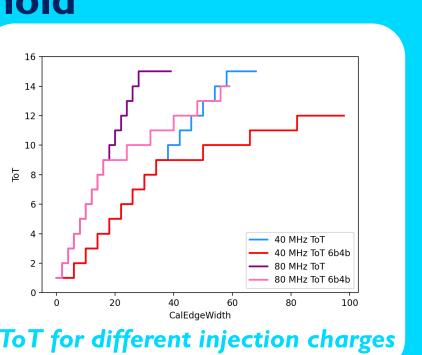

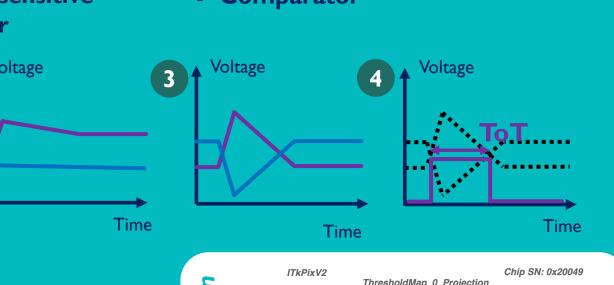

#### Time over Threshold

- ToT is main chip data output during operations

- Several modes of ToT implemented for flexibility

- ToT bug fixed for ITkPixV2

**Single-Event Upset**

#### ITkPix V2

- ATLAS ITkPixV2 chip submitted in April

- Many small changes to improve:

- Stability against single-event transients

- Startup and powering stability

- Improvements and additional monitoring sensors for temperature and radiation

- Received back engineering run wafers

- Validated most chip functionality to work as expected

- → ATLAS Pixel ASIC ready for ITk production

ITK TDR (Apr 2017)

**RD53** Collaboration LOI (Feb 2013)

RD53B design finished (Nov 2019)

**CROCVI** submission (Jun 2021)

ITkPixV2 submission (03/2023)

CROCV2 submission (Oct 2023)

2013

2017 Proto IP 2018

→ ref

RD53A

2019

2020

**2021**

RD53B

2023

2024

RD53C

FE65-P2 and CHIPX prototype chips (Dec 2015)

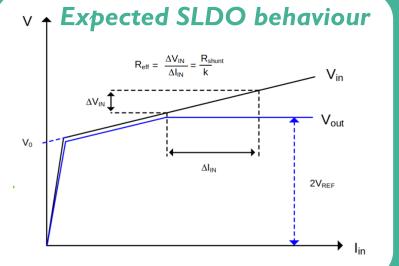

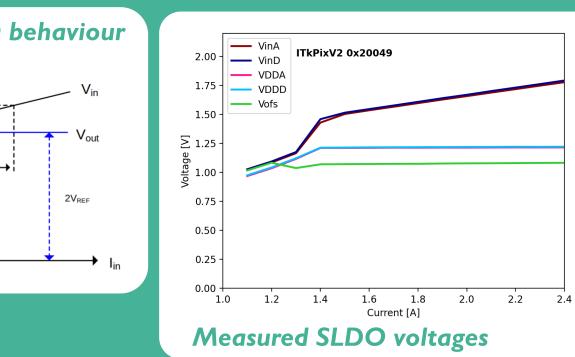

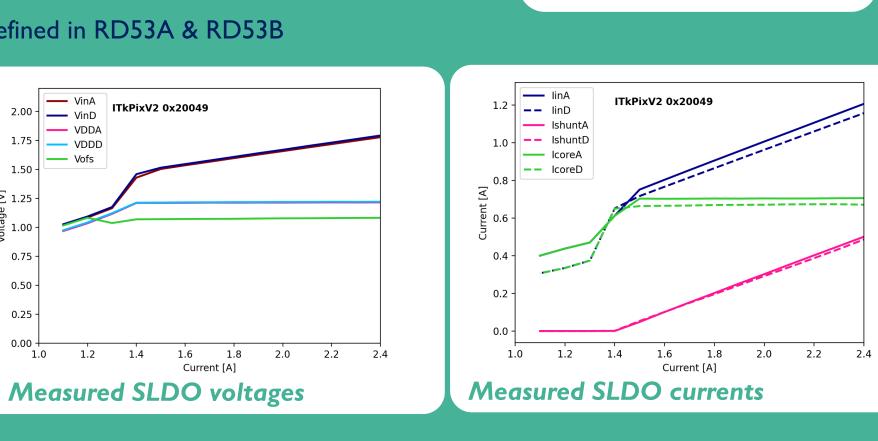

# **Serial Powering: SLDO**

- ITkPixVI modules will be operated in a serial power configuration, suppying a

- Motivation: reduce the number of cables and material in the detector

- Solution: **SLDO** circuit, which powers the main load (the chip) and the internal load (shunt element)

- · Shunt element is designed such that it achieves the required input current, regardle of what the chip does

**SLDO** circuit

**RD53A AFE review** & design validation finished (12/2018)

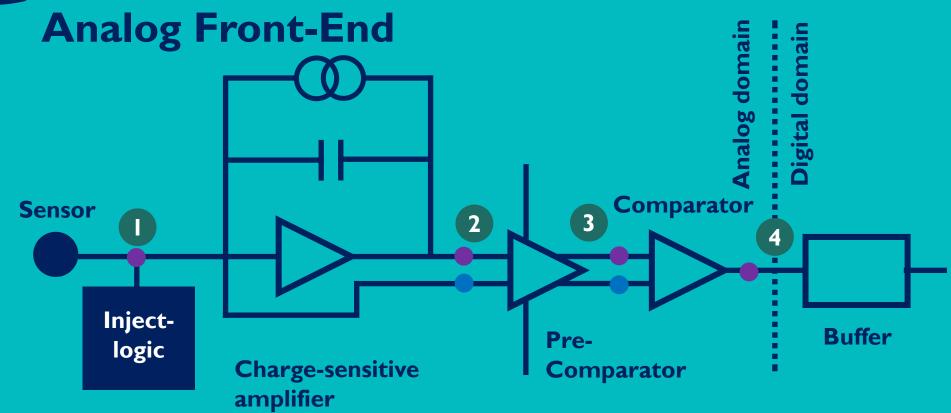

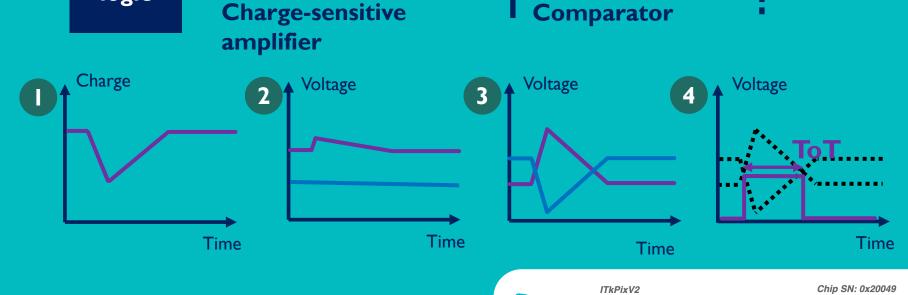

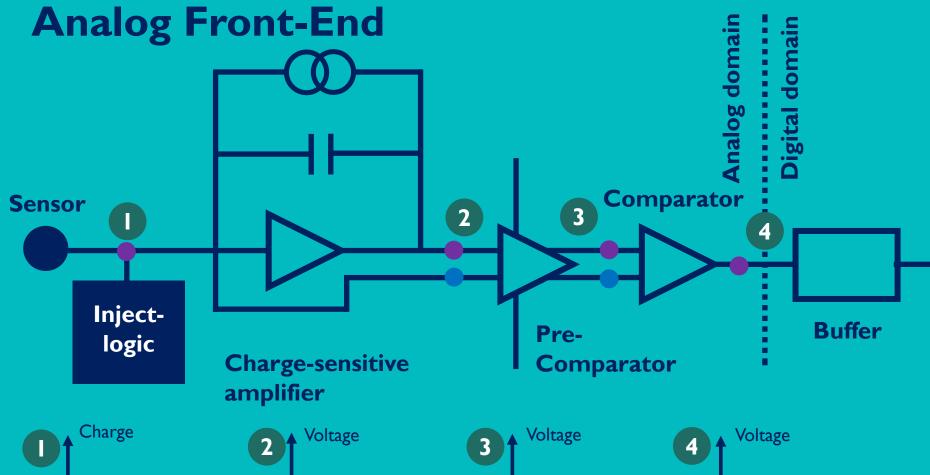

- Differential analog front-end chosen for the ATLAS pixel readout chip

- comparator and digitized

- Threshold adjustable globally and per pixel

**ITkPixVI** submission (03/2020)

18000  $\frac{1}{2}$   $\frac{1}{2}$

14000 - Overflow = 1

10000

12000 Underflow = 0

- Time-over-threshold determined by

# ITkPixVI.I submission (10/2020)

# **ITkPixVI**

- ATLAS ITkPixVI chip submitted in March

- Found a serious issue in the time-over-threshold (ToT) memory

2022

- Large current for particular configurations of ToT

- Wrong ToT storage and hit loss

- Fix to the mask on the remaining FE wafers, fixing the issue of large leakage current in ITkPixVI.I (but ToT still not useable), submitted in October 2020

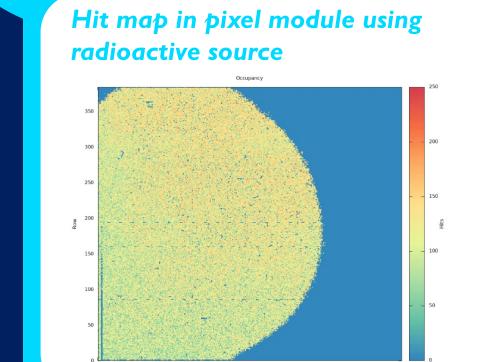

- ITkPixVI characterised over two years in testbench setups, pixel modules (including sensors) and testbeam measurements

- → No major issues found

- ITkPixVI.I will be used as the ITk pre-production readout chip