# ITk Pixel TDAQ for HL-LHC using Optoboard-FELIX interface at LBL

Angira Rastogi, Simone Pagan Griso, Timon Heim

Weekly Instrumentation Meeting Feb 24<sup>th</sup>, 2023

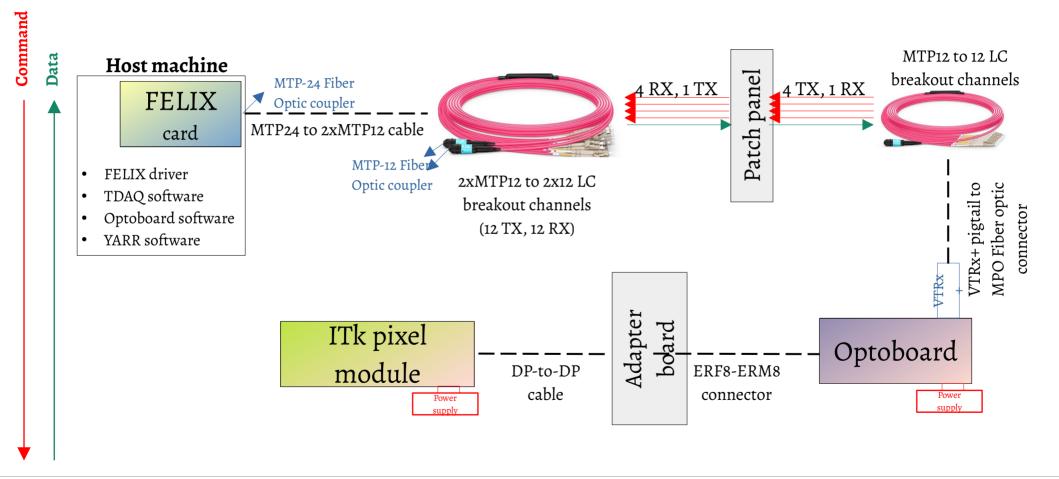

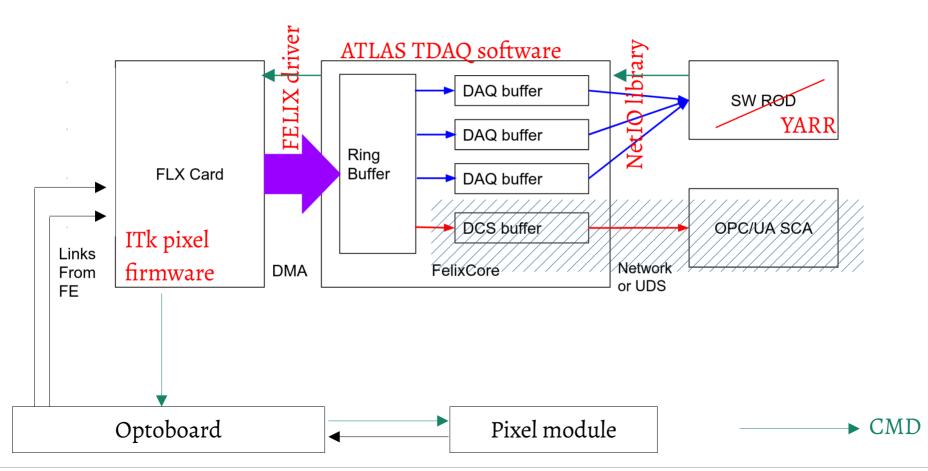

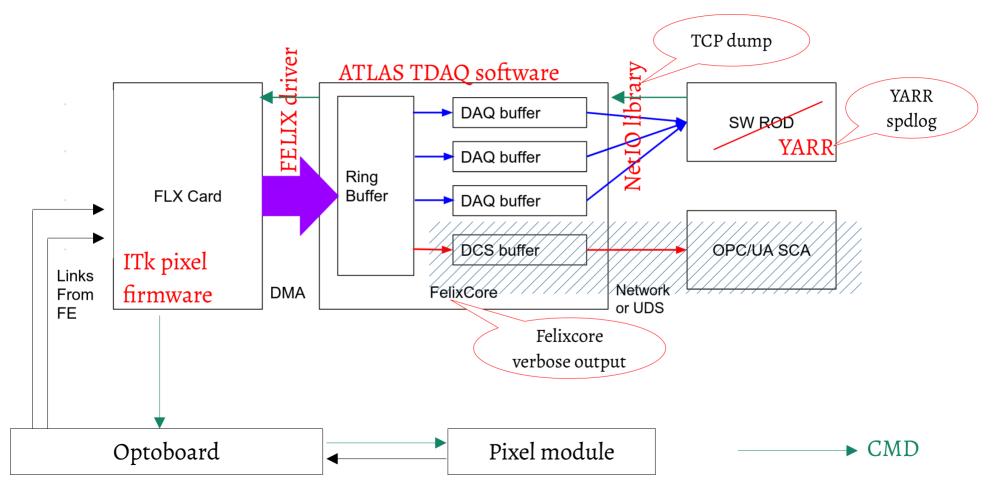

## ITk Pixel TDAQ setup at LBL

Optoboard – ITk pixel module

50B-6038

#### Schematic of the setup

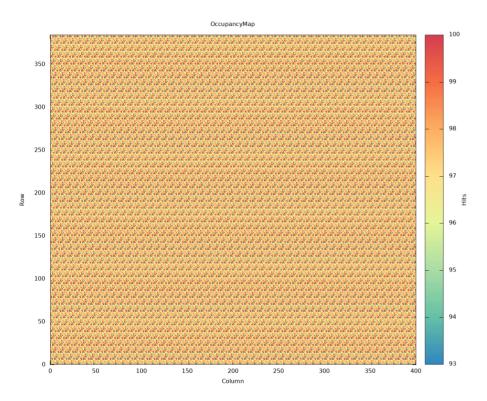

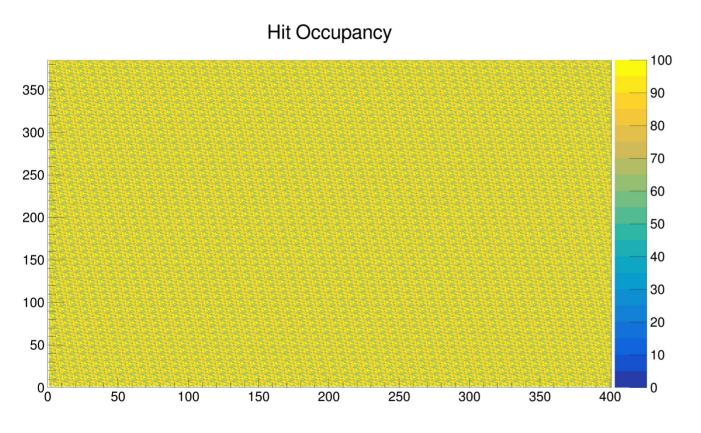

#### Recap: Digital scan

Link

- Software-based trigger generation.

- Wait time of 1 second in StdDataLoop of YARR.

- Trigger frequency = 100 Hz

- Trigger count (injections) = 100

- Number of mask stages = 64

An example of a successful digital scan...

#### The heart of communication

Feb 24, 2023

## Debugging

Feb 24, 2023

Angira Rastogi

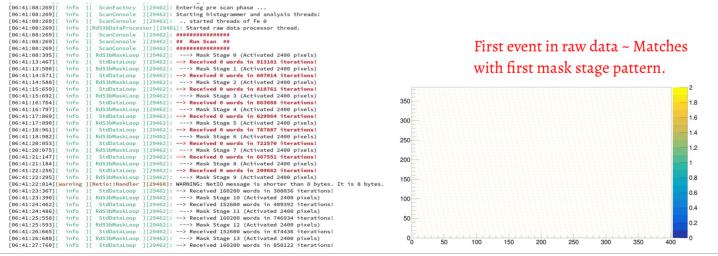

#### Investigating the digital scans

- Software-based trigger generation.

- Wait time of 1 second in

StdDataLoop of YARR.

Varied it up to 5 seconds at which point every mask stage has non-zero occupancy, but then felixcore crashes in between the scan.

- Trigger frequency = 5000 Hz

Increasing the frequency otherwise felixcore server crashes in between the digital scan.

- Trigger count (injections) = 100

- Number of mask stages = 64

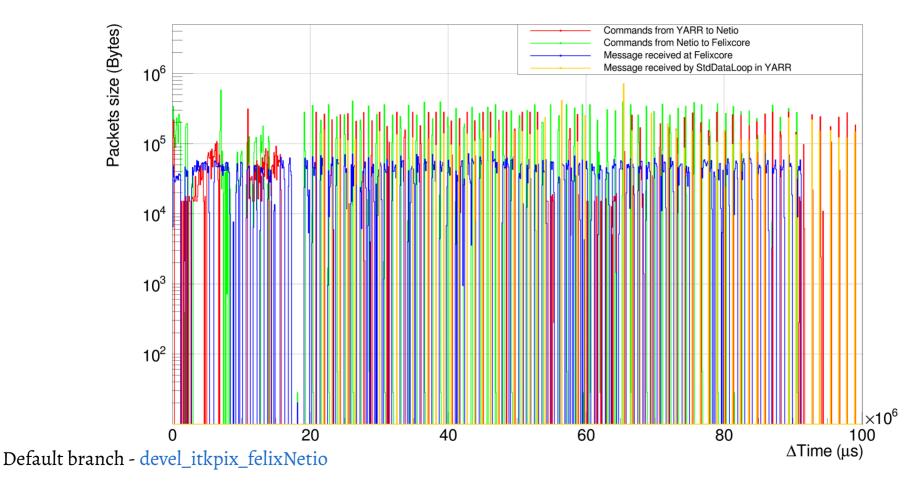

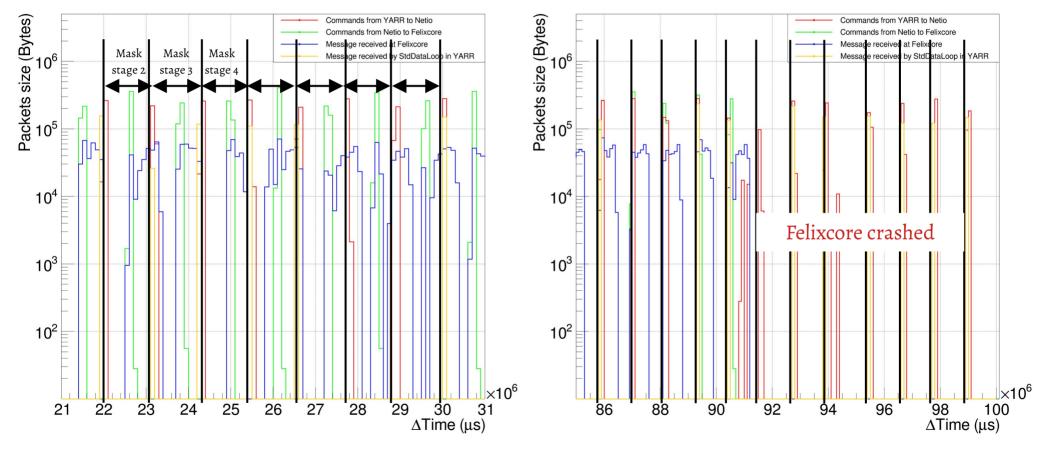

## Timing vs packets: SW triggers

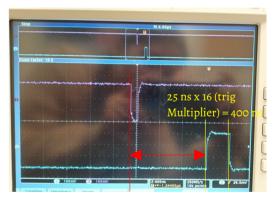

## Switching to FW triggers

BERKELEY LAB

- No raw data seen from the digital scan.

- Packets with valid headers but no payload.

- Varied the delay time and latency in the scan config to adjust the arrival of triggers, still nothing.

- The second secon

- Calibration injection, delay and trigger sequence not set in the FELIX firmware by default.

- Raw data received after setting those registers.

- No calibration injection+trigger sequence was seen in first few mask stages.

1460 ns ~ 58 BXs (Latency)

## Timing vs packets: FW triggers

12

Default branch - devel\_itkpix\_felixNetio

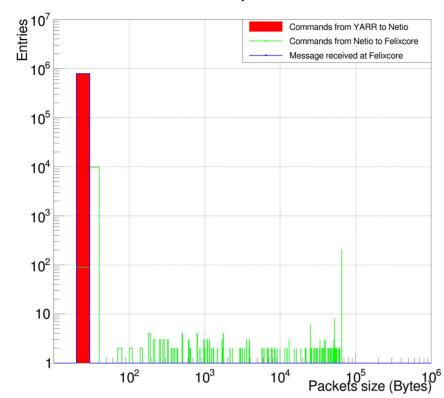

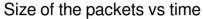

- Command takes a long time to reach the chip. Also, many many encoded packets per command are sent out from YARR to Felixcore.

- Consequences: Felixcore buffer is flushed only after its full, hence takes a long time, and the scan time for that mask stage runs out.

- To resolve this,

- i. Wait longer to collect data back from chip in **StdDataLoop**: less efficient, also very system-dependent. Works only partially in the beginning and then Felixcore crashes.

- ii. No size check for the **NetioTxCore** buffer from YARR exists in the current version. Instead of sending out messages from YARR FiFo to Felixcore constantly, we can aggregate the messages so that command reaches the chip faster and in its entirety.

iii. Can also add a maximum wait time in **NetioRxCore** to get the non-null raw data pointers for every mask stage. Same issues as i.

Instead, a different implementation of this exists from the strip side – to continue reading out more data by using a feedback from the DataProcessor for approximate size of incoming data.

MR - otoldaie/YARR:devel\_DataFeedback

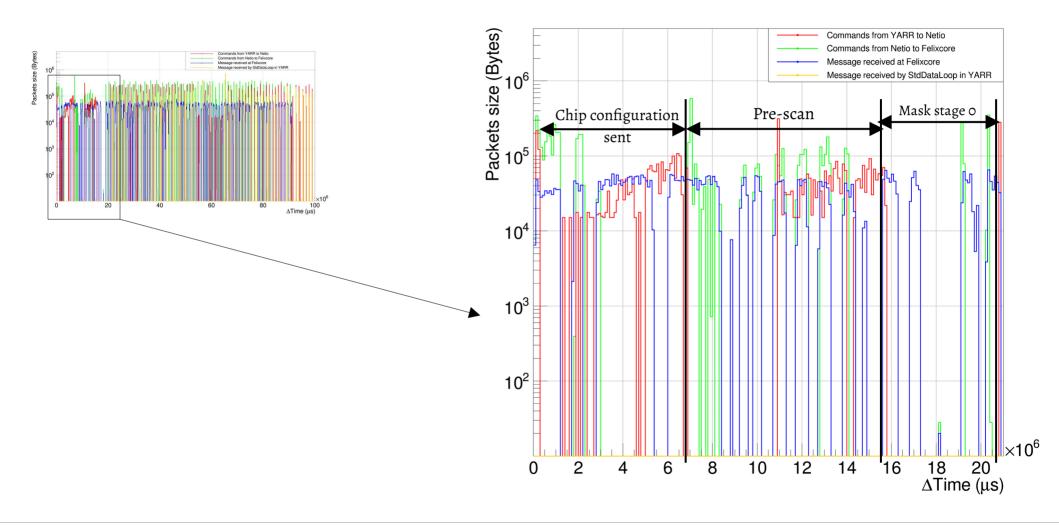

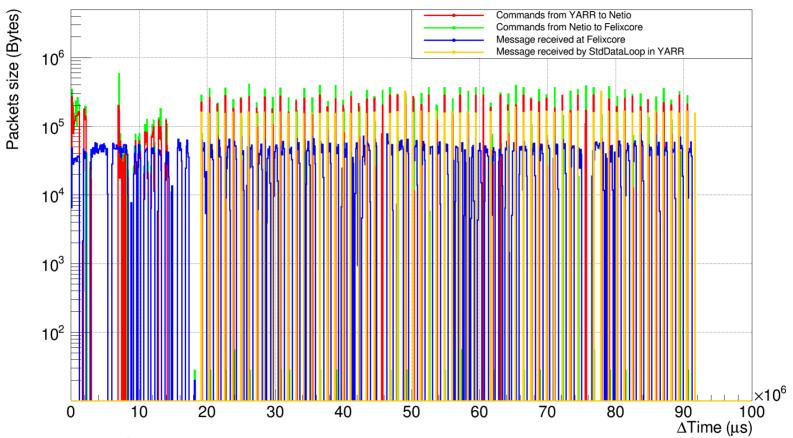

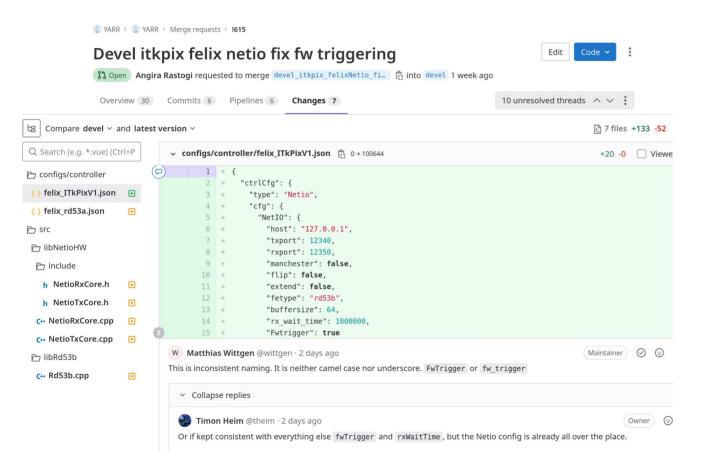

## Fix for FW triggering

- Through releaseFifo(), sending out longer command messages from YARR to felixcore.

- Using IsCmdEmpty() to flush the buffer, if not found empty in the end.

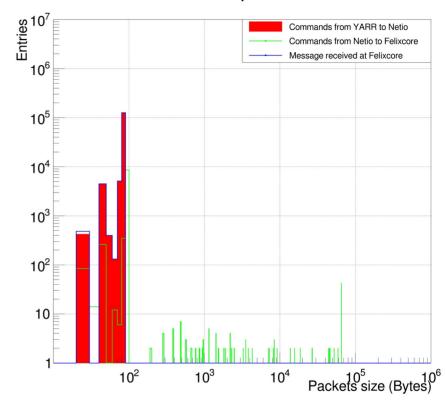

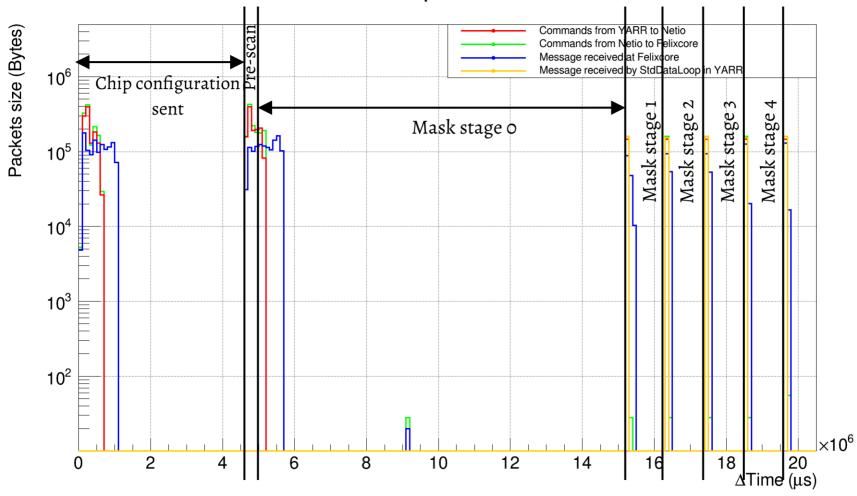

#### Size of packets

Default branch - devel\_itkpix\_felixNetio

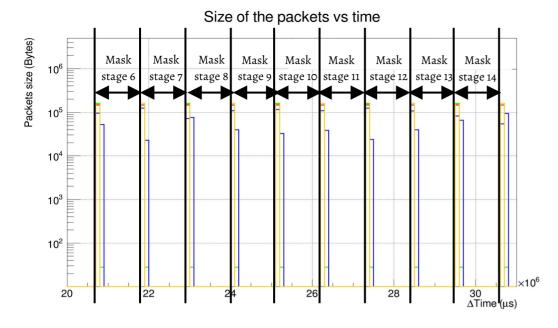

#### Size of packets

New branch - devel\_itkpix\_felixNetio\_fixFWtrigger

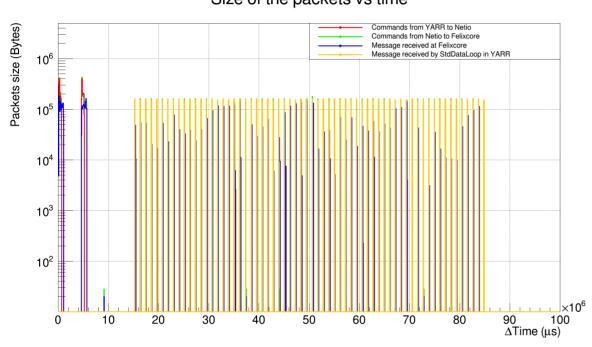

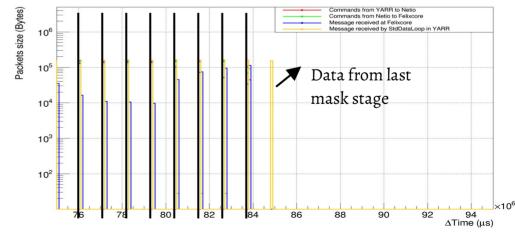

#### FW triggers: New results

17

New branch - devel\_itkpix\_felixNetio\_fixFWtrigger

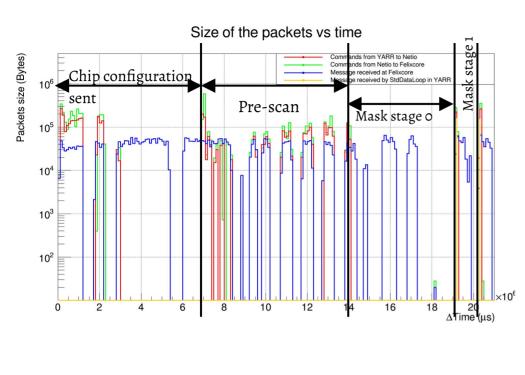

#### Size of the packets vs time

#### Next steps

- Cross verifying the merge request which fixes the firmware trigger, especially changes done in the NetioTxCore, with the strips community.

- Verify the other hidden latencies which could cause delays in sending out the commands such as with network, ethernet or with the host machine.

- Check with other pixel SCCs, if the changes work.

- Understand the timing plots, try to optimize the limit on the buffer size and wait time in StdDataLoop.

- Enable FELIX firmware to read the chip configuration registers (right now its bypassed through the ServiceEnable=0).

- To implement the data processor feedback changes for ITk pixel DAQ.

- Finally, move to using quad modules.