# YARR PCIe Firmware optimisation

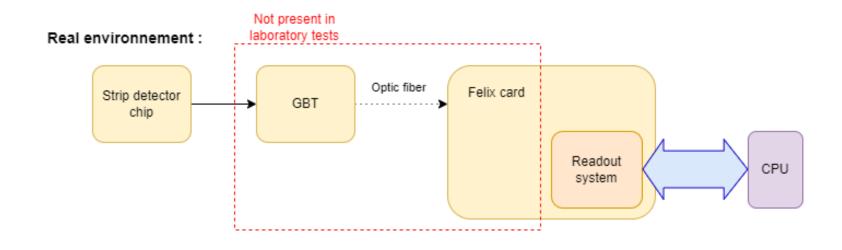

#### **YARR**

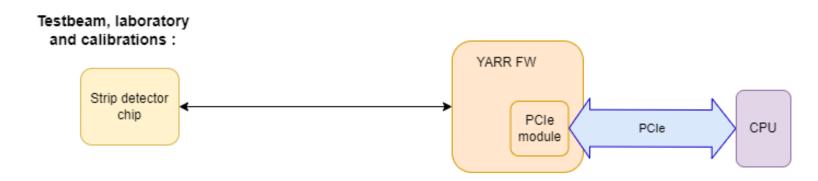

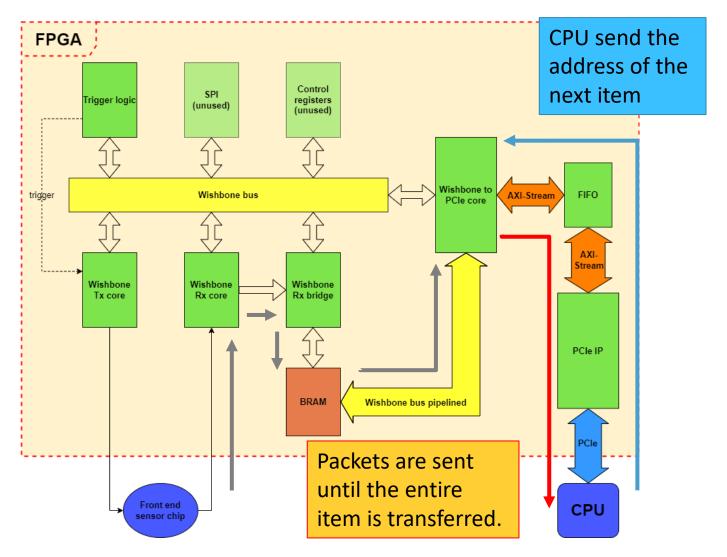

### **FPGA**

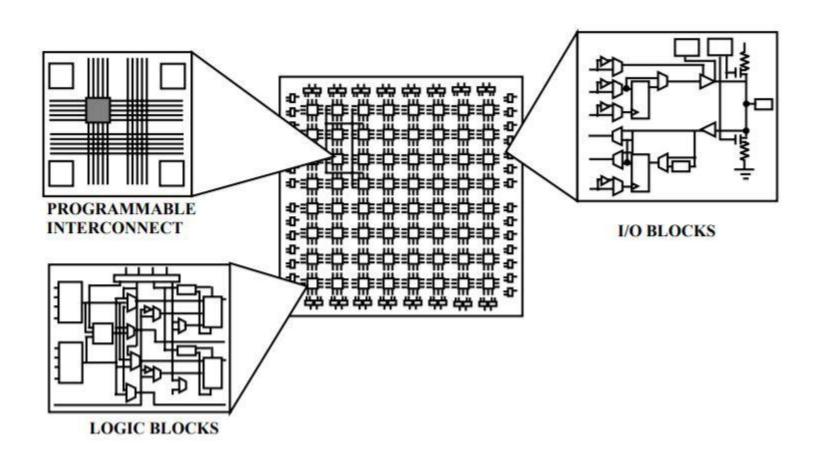

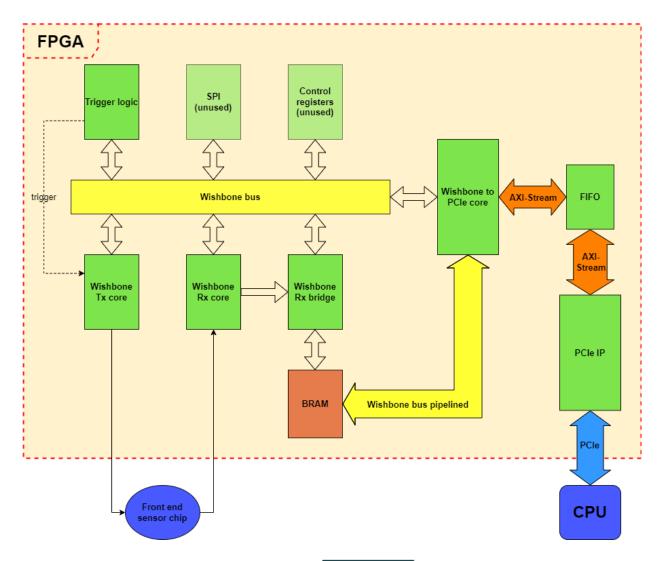

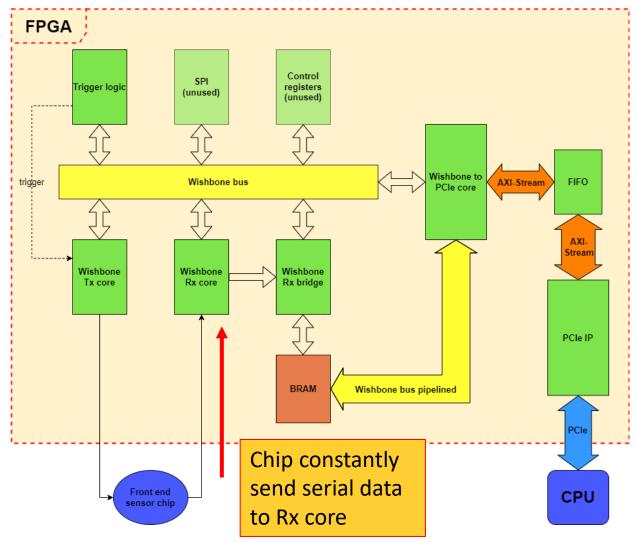

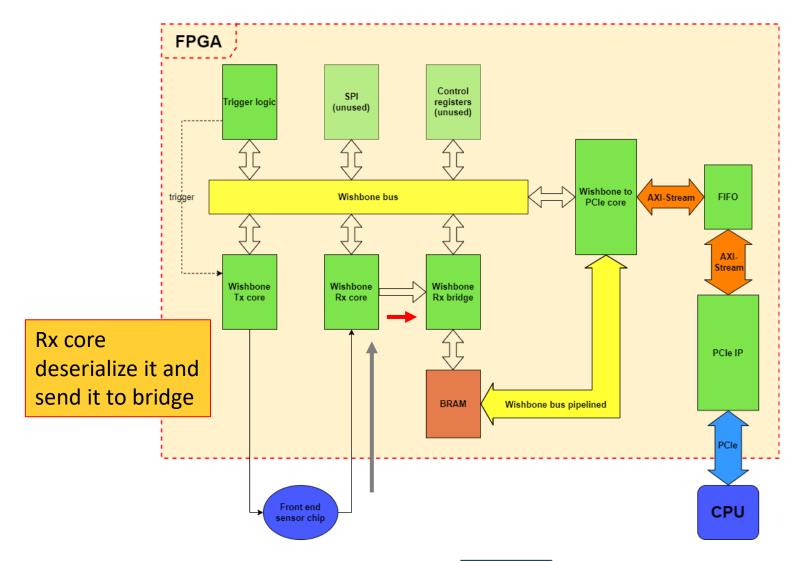

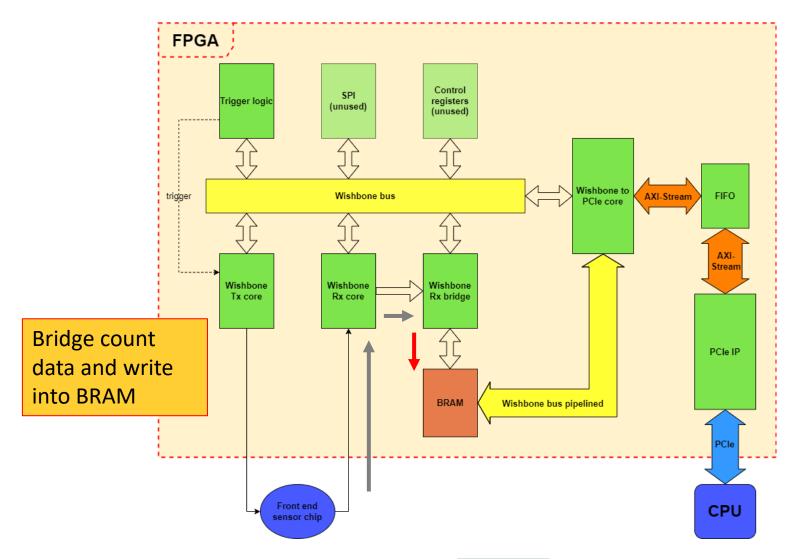

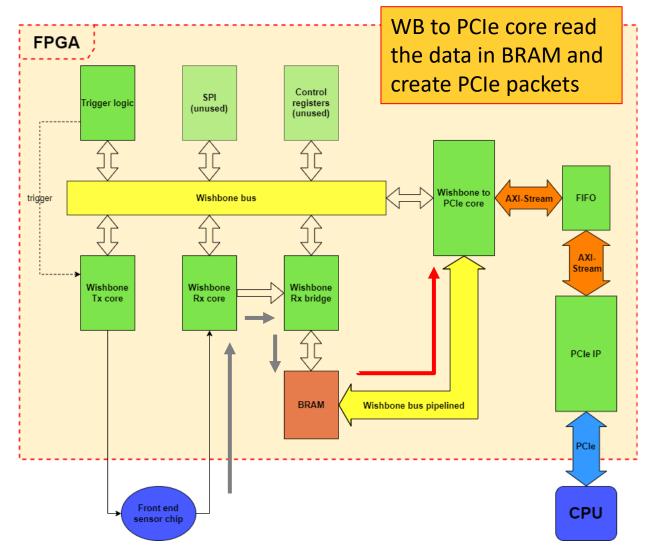

#### Wishbone bus

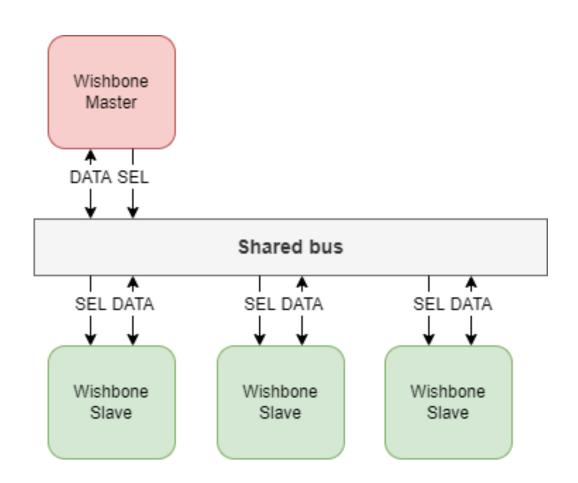

#### Firmware architecture

MASTER OF SCIENCE IN ENGINEERING

MASTER OF SCIENCE IN ENGINEERING

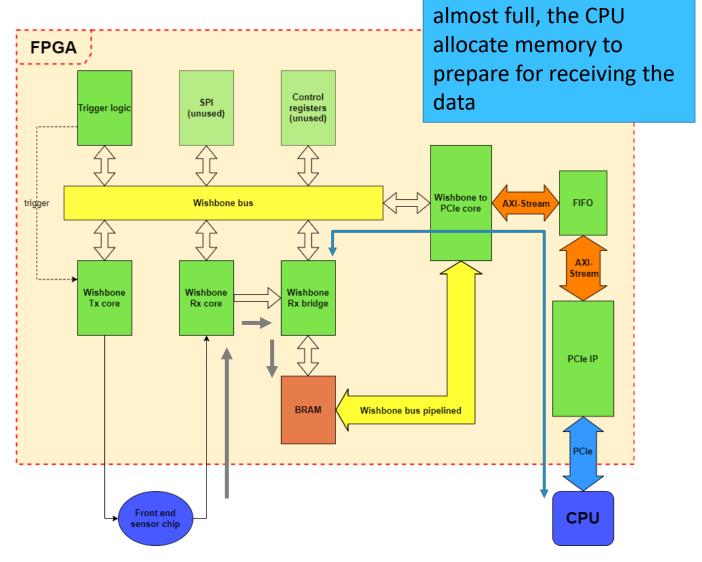

When the BRAM is

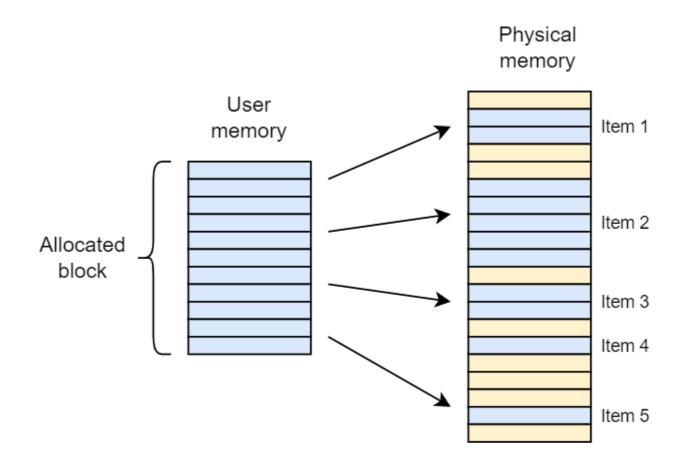

# **Memory allocation**

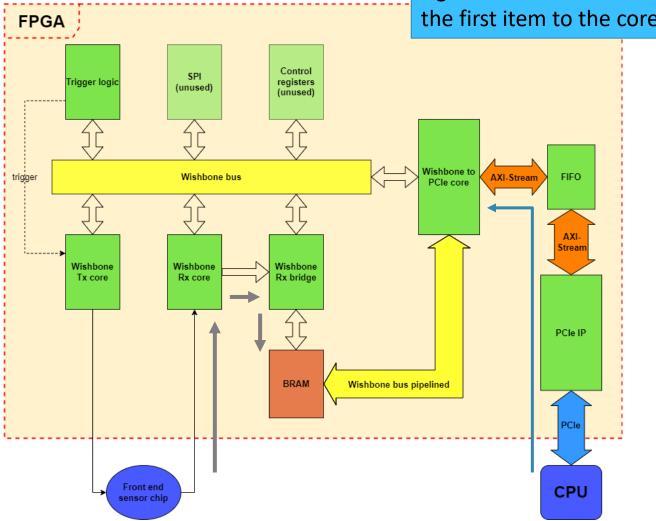

The CPU send the start signal and the address of the first item to the core

MASTER OF SCIENCE IN ENGINEERING

#### Issues

- Important delay between the request of the next item by the FPGA and its reception. Solution -> Request the whole list adresses at once and store them

- Wishbone bus cannot go higher than 160Mhz without having timing issues.

Solution -> Figure out what's wrong and fix it

## Goals of my project

- Analysis of the bottlenecks

- Improvement of the readout speed

- Documentation of the system

IN ENGINEERING

## **Questions?**