#### Moore's Law in 2014: Implications to System-on-a-Chip (SoC) Design

Issy Kipnis

Sr. Principal Engineer, Intel Corporation

September 2014

# Agenda

- Silicon technology

- Introduction to SoC

# **Traditional MOSFET scaling**

| Device or Circuit Parameter  | Scaling Factor | ·                      |

|------------------------------|----------------|------------------------|

| Device dimension tox, L, W   | $1/\kappa$     | VOLTAGE,V WIRING       |

| Doping concentration Na      | κ              |                        |

| Voltage V                    | $1/\kappa$     | GATE J                 |

| Current I                    | $1/\kappa$     | SOURCE CALORAIN        |

| Capacitance $\mathcal{E}A/t$ | 1/K            | Yox xp                 |

| Delay time/circuit VC/I      | $1/\kappa$     | - L-+                  |

| Power dissipation/circuit VI | $1/\kappa^2$   | P SUBSTRATE, DOPING NA |

| Power density VI/A           | 1              |                        |

R. Dennard, IEEE JSSC, 1974

## **Traditional MOSFET scaling**

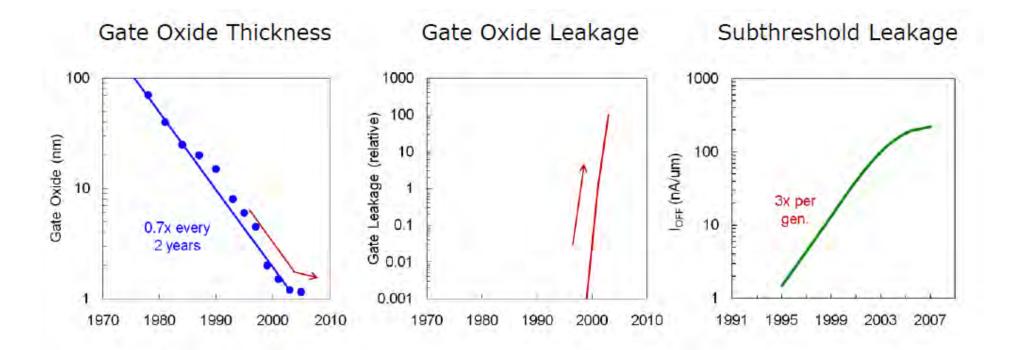

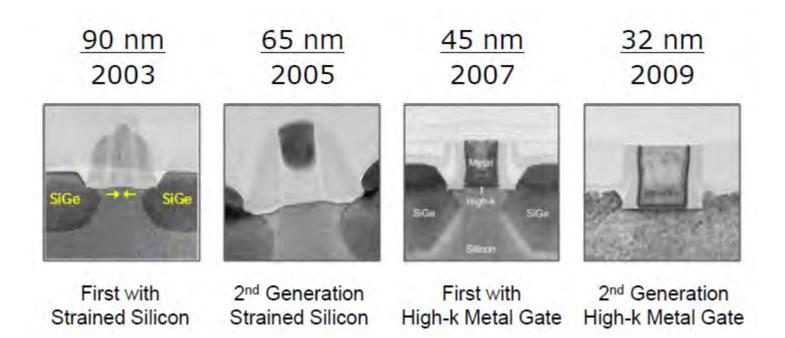

• Traditional MOSFET scaling ran out of steam in the early 2000's

(intel)

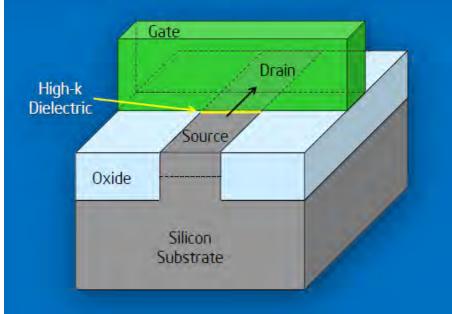

• If traditional methods don't work, then innovate!

#### **Transistor Innovation**

Continued innovation in transistor materials and structure are essential to continued scaling

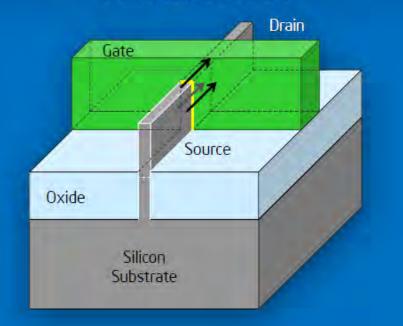

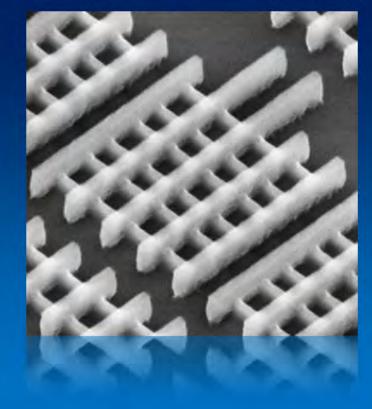

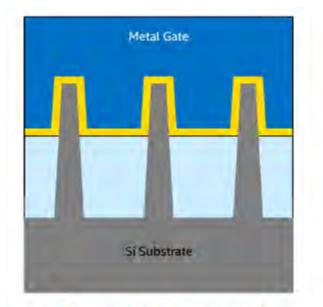

#### Transistors have entered the 3<sup>rd</sup> dimension

#### Standard

Traditional 2-D planar transistors form a conducting channel in the silicon region under the gate electrode when in the "on" state

#### **Tri-Gate**

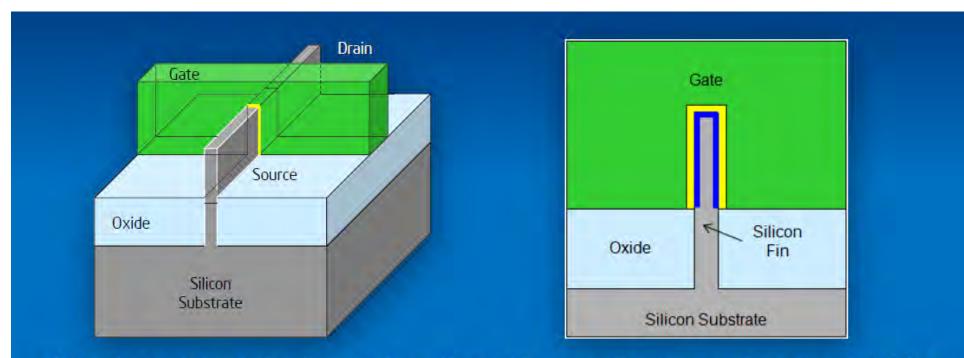

3-D Tri-Gate transistors form conducting channels on three sides of a vertical fin structure

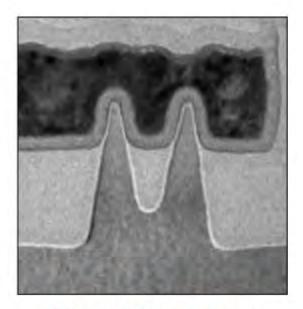

# Tri-gate structure enables fully depleted operation without SOI

Gate electrode controls silicon fin from three sides, providing improved sub-threshold slope

Inversion layer area increased for higher drive current and reduced gate delay

Process cost increased by 2-3% vs 10% for SOI wafers

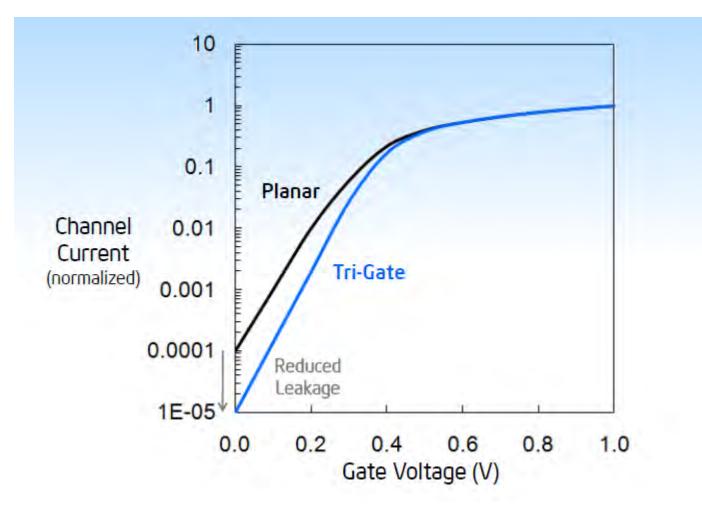

# Fully depleted tri-gate transistors reduce leakage current

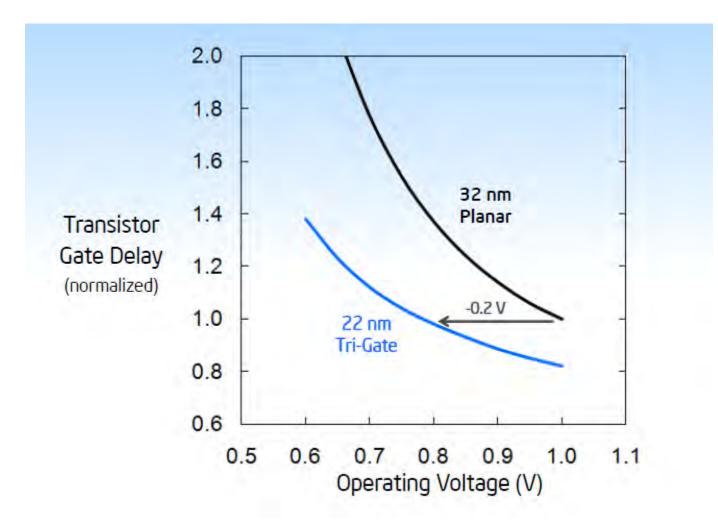

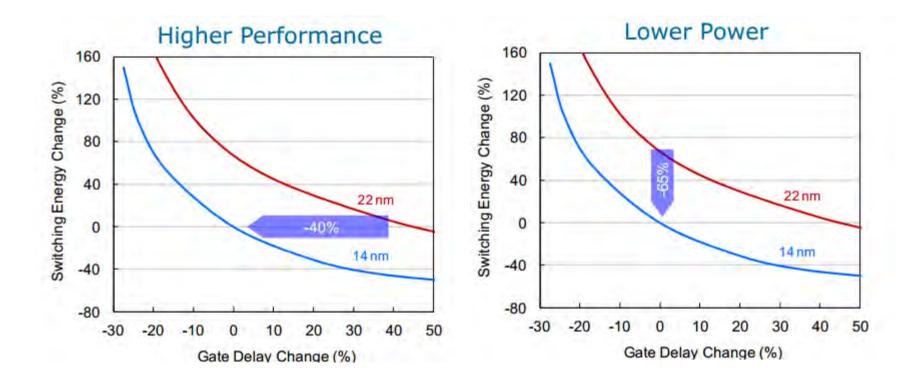

#### Improved performance at high-voltage and unprecedented performance gain at low-voltage

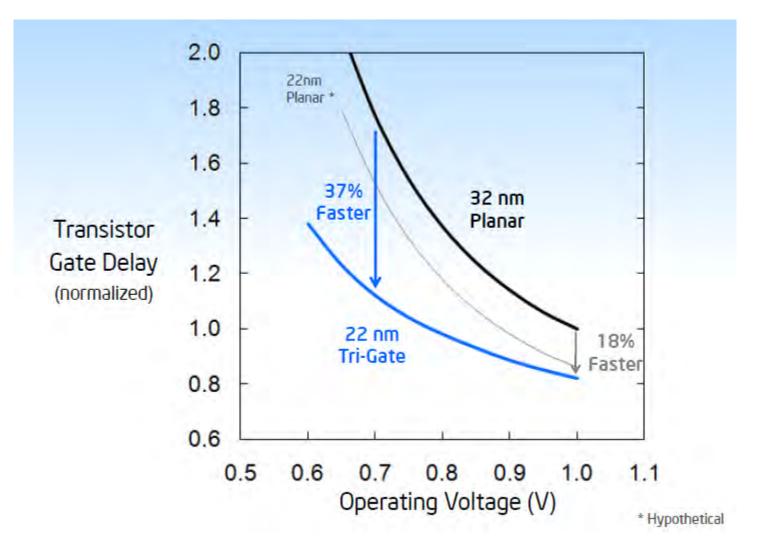

# 22 nm tri-gate transistors reduce active power by up to >50%

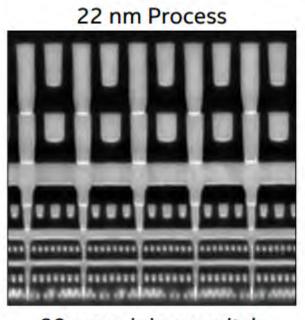

## Tri-gate transistors in 22nm

#### 32 nm Planar Transistors

#### 22 nm Tri-Gate Transistors

(intel)

Source: Intel 2011

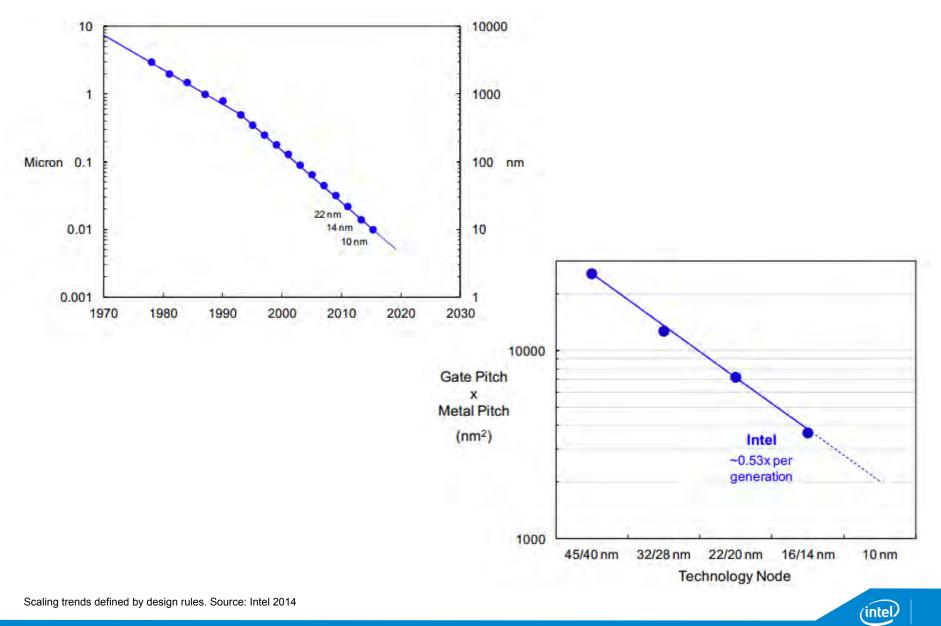

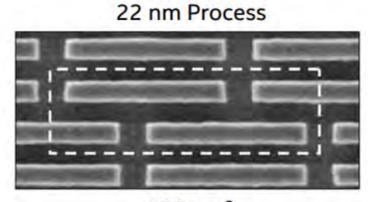

### Scaling trends

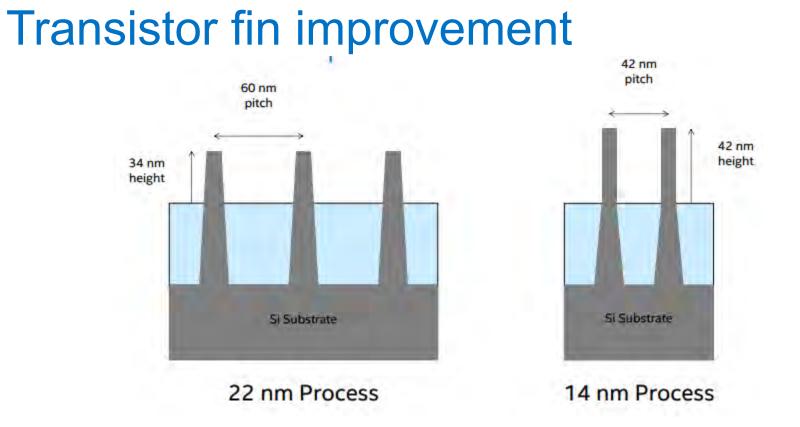

- Tighter fin pitch for improved density

- Taller and thinner fins for increased drive current and performance

- Reduced number of fins for improved density and lower capacitance

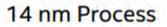

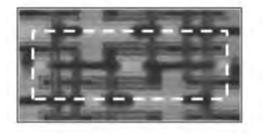

## **Transistor fin improvement**

#### 22 nm 1<sup>st</sup> Generation Tri-gate Transistor

14 nm 2<sup>nd</sup> Generation Tri-gate Transistor

#### Transistor fin improvement

22 nm 1<sup>st</sup> Generation Tri-gate Transistor

14 nm 2<sup>nd</sup> Generation Tri-gate Transistor

#### Interconnects

80 nm minimum pitch

52 nm (0.65x) minimum pitch

Better than normal interconnect scaling

## SRAM memory cells

.108 um<sup>2</sup> (Used on CPU products) 14 nm Process

.0588 um<sup>2</sup> (0.54x area scaling)

1

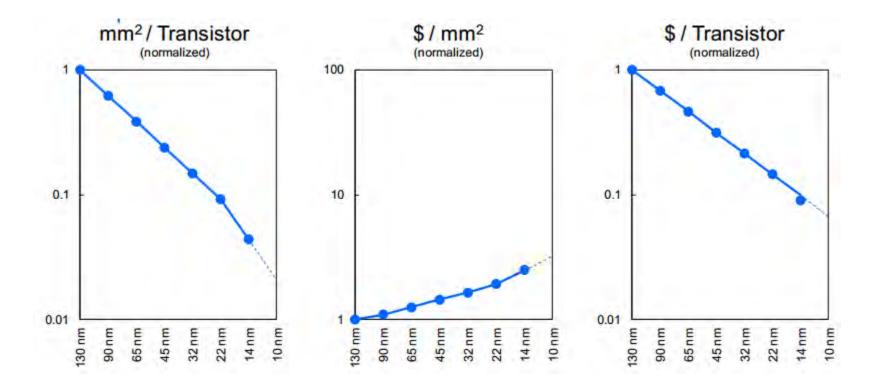

### Cost per transistor

- Better than normal area scaling by using advanced double patterning techniques

- Wafer cost increasing due to added masking steps

- Still delivering lower cost per transistor

#### Transistor improvements continues in14nm

# Agenda

- Silicon technology

- Introduction to SoC

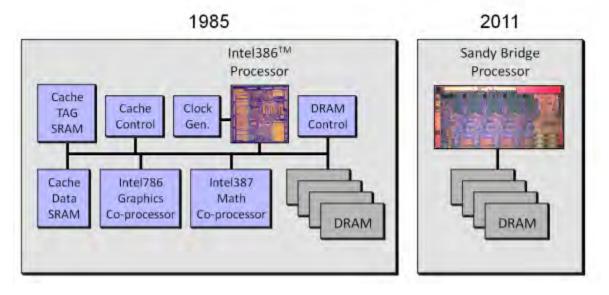

# System integration

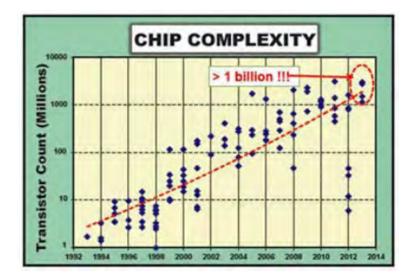

- Moore's law continues to enable ever increasing levels of chip complexity

- Creates a paradigm in system level HW/SW codesign

## What is a SoC?

- System-on-a-chip refers to integrating all components of a computer or other electronic system into a single integrated circuit (IC) chip. It may contain digital, analog, mixed-signal, and often radio-frequency functions – all on a single chip substrate. (Wikipedia)

- This consolidation enables smaller, thinner devices while reducing the amount of power required for the device, increasing battery life and making possible always-on and always-connected functionality.

- A SoC consists of both the hardware and the software that controls the microcontroller, microprocessor or DSP cores, peripherals and interfaces.

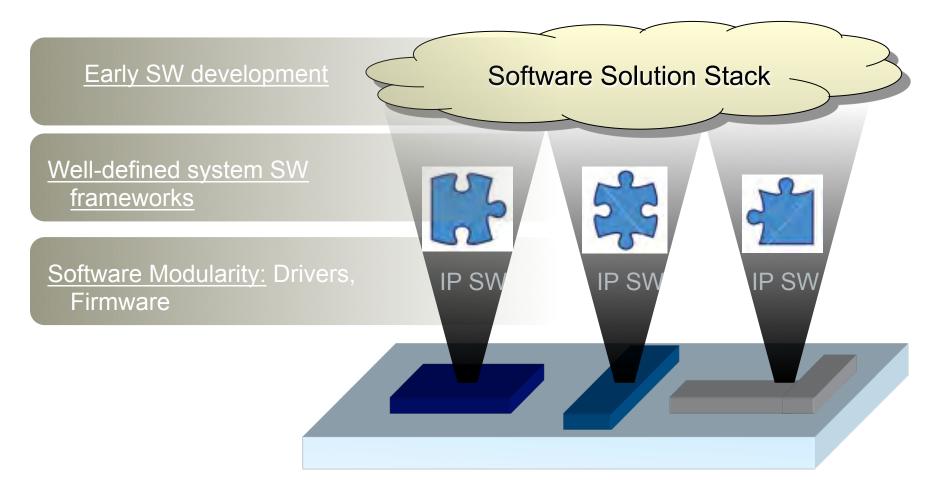

# SoC challenge #1 – beyond silicon: software and system

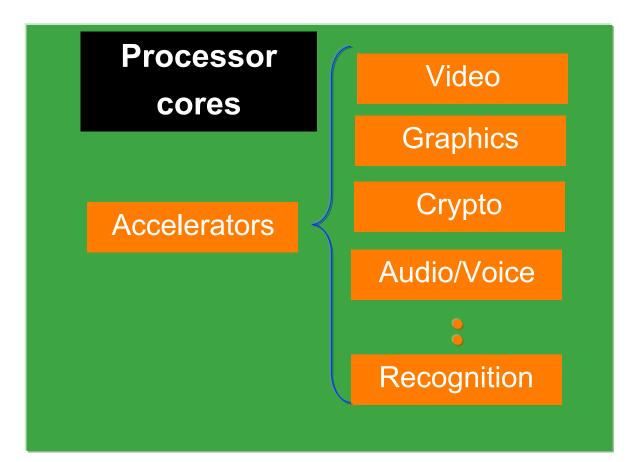

#### SoC challenge #2 - Dealing with heterogeneity

#### SoC challenge #3 – on-die interconnect

#### Apply tools used for off-chip networks?

- Design space: topology, switching, routing, flow control, virtualization

- Cost metrics: wire bisection, switch size, total power, total devices

- Performance Metrics: throughput, latency, traffic structure independence/robustness, hot spot performance, quality of service

intel

Important differences -- Integration, costs, technology, workloads, energy... tradeoffs reopened

#### SoC challenge #4 – SoC realization

- A critical gap between SoC development process and the process of conceptualizing and analyzing designs at a system level (a high level of abstraction) without the restrictions of physical operating constraints

- Software application developers must have access to the system level implementation before the SoC is actually manufactured to test and debug the software and uncover any SoC architectural problems

- No connection between these two different levels of abstractions.

- How to ensure system architectural intent or design coherence?

## SoC: New Discipline

- Map the system level information to the next level of abstraction

- Need tools to guide the design from concept to implementation and ensure design coherence from one level to the next

- Must make available a complete hardware/software platform that will provide all the necessary support for end-user applications

- Need Hardware-Software Co-Design: meeting of system-level objectives by exploiting the tradeoffs between hardware and software in a system through concurrent design

- Concurrent development: Hardware and Software Developed at the same time on parallel paths

- Integrated development: Interaction between hardware and software development to produce design meeting performance criteria and functional specs.

## Summary

- In 2014, Moore's law is alive and well!

- Scaling requires continue innovation in device materials and structures

- Moore's law enabling ever increasing levels of chip complexity

- Creating a new paradigm of system level HW/SW codesign

- SoC as a new discipline driving the industry to develop new competencies and tools

#### Legal Notices and Disclaimers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http:// www.intel.com/design/literature.htm

All products, computer systems, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

Intel product plans in this presentation do not constitute Intel plan of record product roadmaps. Please contact your Intel representative to obtain Intel's current plan of record product roadmaps.

This document contains information on products in the design phase of development.

Material in this presentation is intended as product positioning and not approved end user messaging.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Results have been estimated based on internal Intel analysis and are provided for informational purposes only. Any difference in system hardware or software design or configuration may affect actual performance.

Results have been simulated and are provided for informational purposes only. Results were derived using simulations run on an architecture simulator or model. Any difference in system hardware or software design or configuration may affect actual performance.

Intel does not control or audit the design or implementation of third party benchmark data or Web sites referenced in this document. Intel encourages all of its customers to visit the referenced Web sites or others where similar performance benchmark data are reported and confirm whether the referenced benchmark data are accurate and reflect performance of systems available for purchase.

Code names are internal project names used solely as identifiers and are not intended to be used as trademarks or publicly disseminated.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2014 Intel Corporation. All rights reserved.

### **Risk Factors**

The above statements and any others in this document that refer to plans and expectations for the second guarter, the year and the future are forward-looking statements that involve a number of risks and uncertainties. Words such as "anticipates," "expects," "intends," "plans," "believes," "seeks," "estimates," "will," "should" and their variations identify forward-looking statements. Statements that refer to or are based on projections, uncertain events or assumptions also identify forward-looking statements. Many factors could affect Intel's actual results, and variances from Intel's current expectations regarding such factors could cause actual results to differ materially from those expressed in these forward-looking statements. Intel presently considers the following to be important factors that could cause actual results to differ materially from the company's expectations. Demand for Intel's products is highly variable and, in recent years, Intel has experienced declining orders in the traditional PC market segment. Demand could be different from Intel's expectations due to factors including changes in business and economic conditions; consumer confidence or income levels; customer acceptance of Intel's and competitors' products; competitive and pricing pressures, including actions taken by competitors; supply constraints and other disruptions affecting customers; changes in customer order patterns including order cancellations; and changes in the level of inventory at customers. Intel operates in highly competitive industries and its operations have high costs that are either fixed or difficult to reduce in the short term. Intel's gross margin percentage could vary significantly from expectations based on capacity utilization; variations in inventory valuation, including variations related to the timing of qualifying products for sale; changes in revenue levels; segment product mix; the timing and execution of the manufacturing ramp and associated costs; excess or obsolete inventory; changes in unit costs; defects or disruptions in the supply of materials or resources; and product manufacturing quality/yields. Variations in gross margin may also be caused by the timing of Intel product introductions and related expenses, including marketing expenses, and Intel's ability to respond quickly to technological developments and to introduce new products or incorporate new features into existing products, which may result in restructuring and asset impairment charges. Intel's results could be affected by adverse economic, social, political and physical/infrastructure conditions in countries where Intel, its customers or its suppliers operate, including military conflict and other security risks, natural disasters, infrastructure disruptions, health concerns and fluctuations in currency exchange rates. Intel's results could be affected by the timing of closing of acquisitions, divestitures and other significant transactions. Intel's results could be affected by adverse effects associated with product defects and errata (deviations from published specifications), and by litigation or regulatory matters involving intellectual property, stockholder, consumer, antitrust, disclosure and other issues, such as the litigation and regulatory matters described in Intel's SEC filings. An unfavorable ruling could include monetary damages or an injunction prohibiting Intel from manufacturing or selling one or more products, precluding particular business practices, impacting Intel's ability to design its products, or requiring other remedies such as compulsory licensing of intellectual property. A detailed discussion of these and other factors that could affect Intel's results is included in Intel's SEC filings, including the company's most recent reports on Form 10-Q. Form 10-K and earnings release.