# Handshake Protocol and Channel Bonding in Yarr firmware

Lauren Choquer - University of Washington ACME Lab / LBNL Timon Heim - LBNL

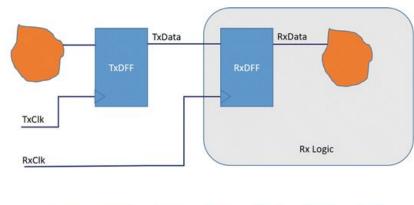

#### Metastability

- Asynchronous signal being passed between clock domains of different frequencies

- System can be sent into an unknown state for an unbounded amount of time (halfway between 0 or 1)

- Problem if setup (before clock edge) or hold (after clock edge) periods violated

- One metastable signal can affect entire system

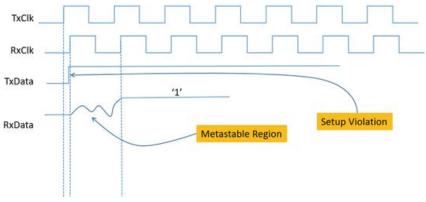

#### **Metastability in Yarr-fw**

- Conflicting clock domains with status registers passing in between

- Metastable signals changing rarely

- In theory, not much of a problem for our system

- Still must be resolved to pass timing analysis at proper clock speeds

#### Setup

Worst Negative Slack (WNS): -3.564 ns

Total Negative Slack (TNS): -3802.759 ns

Number of Failing Endpoints: 1671

Total Number of Endpoints: 72860

Timing constraints are not met.

# Yarr-fw Wishbone Express

- High-speed, flexible interconnect

- AXI-stream -> wishbone -> firmware logic blocks

- Unrelated clock frequencies

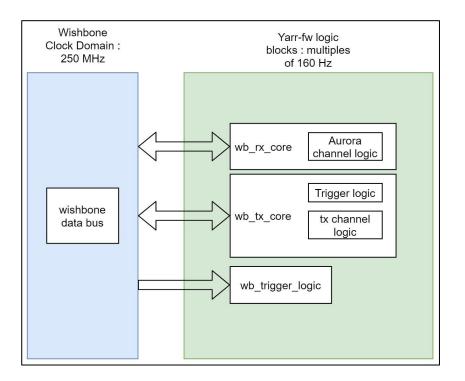

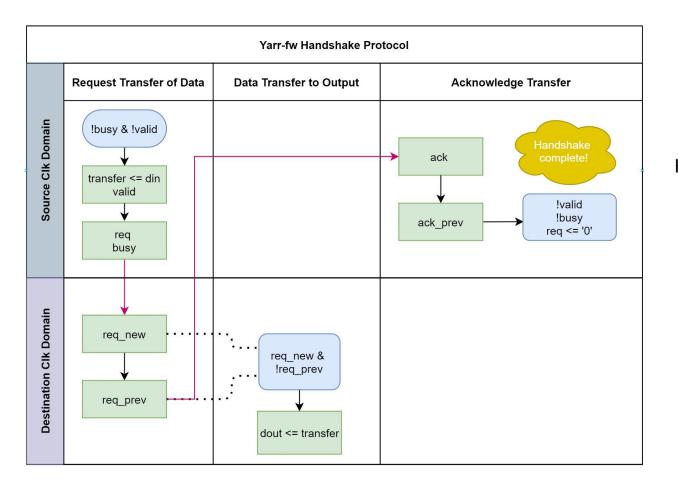

#### **Handshake Protocol**

- Ideal synchronization method for crossing between clocks of non-integer ratios

- Preferable for multi-bit signals compared to flip-flop chain synchronizer

- Lower resource utilization than FIFOs, preferable in Yarr-fw case

#### Key differences:

- Addition of transfer data register for multi-bit signals

- Pre-transfer valid signal

- Raise 'acknowledge' flag once data transfer is complete

#### **Current Status of Handshake**

- Implemented in Yarr-fw

- Code has been reviewed, will be merged soon

- Passes timing constraints in Xilinx Vivado

- Has been stress-tested on kc705 FPGA

- Next step: scanConsole verification using RD53A

#### **KC705 Yarr-fw configuration**

- Yarr-fw previously set up only for xpressk7 and tef1001 boards

- Added support for kc705 hardware

- New set of constraint files

- Flash script updated

- Currently debugging with RD53A

**CERN SPEC (Spartan 6)**

Xilinx KC705

ReflexCES XpressK7

Trenz TEF-1001

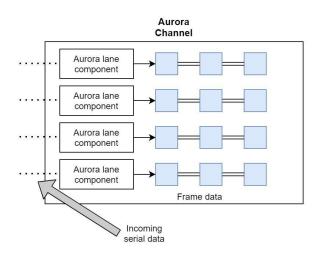

#### **Aurora in Yarr-fw**

- Aurora interface: "lightweight link-layer protocol that can be used to move data point-to-point across one or more high-speed serial lanes"

- Using 64/66b encoding

- Yarr-fw uses up to 4 Aurora channels

- Each consisting of up to 4 lanes

- Each lane produces 64b-frames of data/commands with 2b headers

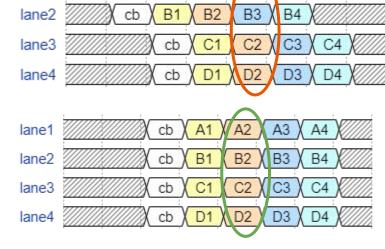

#### **Channel Bonding**

Lanes can become out of sync:

lane1

For RD53B, a **channel bonding** process is needed in order to realign them:

Correct data alignment

Misaligned data

### **Channel Bonding Implementation**

- Channel bonding command frames:

- o command header = 0b10

- $\circ$  idle tag = 0x78

- channel bonding flag raised high

- Method:

- Detect channel bonding frames

- Based on CB frames, detect which lanes are early compared to rest

- Delay early lanes using shift register

```

rx clk

data_in[0] cb

A2 X A3 X

Unbonded Lanes

is cb frame[0]

is cb frame prev[0]

B3 X B4

data in[1] B0

cb

B1 X B2 X

is cb frame[1]

is cb_frame_prev[1]

lane_early[0]

lane_early[1]

Shifted Data

data_sr[0]

cb

A1

data_sr[1] B0

cb X B1 X

data out[0]

A1 X A2 X

A3 X A4

Bonded Lanes

data_out[1] B0

В3

cb

B1 ( B2 )

```

Channel bonding simulation waveform and output logic

## Thanks for listening!

Questions?