# RD53 Status ans Plans Pivel readout integrated circuits

h bh bh k hit had blist it had total bla tand to be the a facilitate between the bill black and blille be a bit black in a bit blist

Pixel readout integrated circuits for extreme rate and radiation

6<sup>th</sup> LHCC Report- Sept. 11, 2019

M. Garcia-Sciveres (LBNL) on behalf of the RD53 Collaboration

# **Previously on RD53**

- Focused R&D to develop pixel chips for both ATLAS and CMS upgrades

- Established in 2013 recognizing that HL-LHC pixel requirements were extremely challenging, yet very similar for both experiment, and a joint effort was the best way to meet them

- Successful R&D culminated in the RD53A prototype chip, fabricated at the end of 2017. This fulfilled the original mandate of RD53.

- RD53A continues to be extensively used by both experiment to prototype their HL-LHC detectors. 110 RD53A wafers have been purchased to date – 3x as many pixels as current ATLAS and CMS combined.

- At the request of the experiments, last year the mandate of RD53 was extended to design the final production chips for ATLAS and CMS

- Keep the design team together.

- Pursue as much as possible a common design to serve the needs of both experiments.

- RD53 has 22 collaborating institutes and many Guests

- ~100 conference talks/proceedings/papers to date

# **The Most Important Aspect of RD53**

The people

# **RD53 Designs and Chips**

- RD53A is the existing prototype

- RD53B is not a physical chip. It is a design library / environment

- The first incarnation of RD53B will be RD53B-ATLAS (which ATLAS calls ItkPix-V1) To be fabricated this fall.

- The second incarnation will be RD53B-CMS, to be fabricated in 2020 (may be able to take advantage of initial RD53B-ATLAS test results)

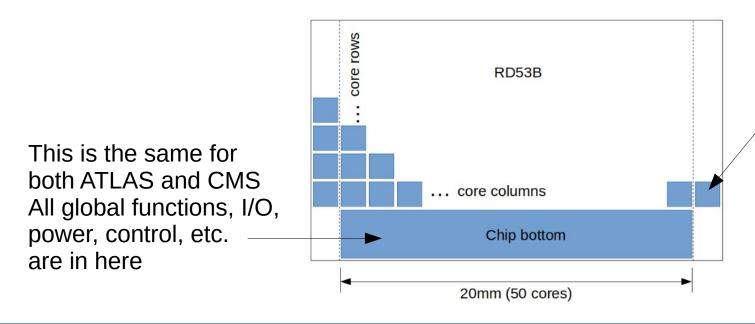

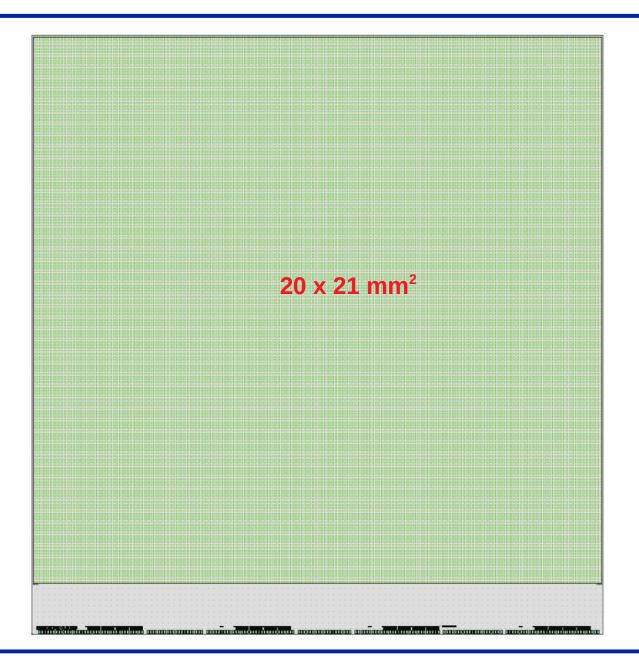

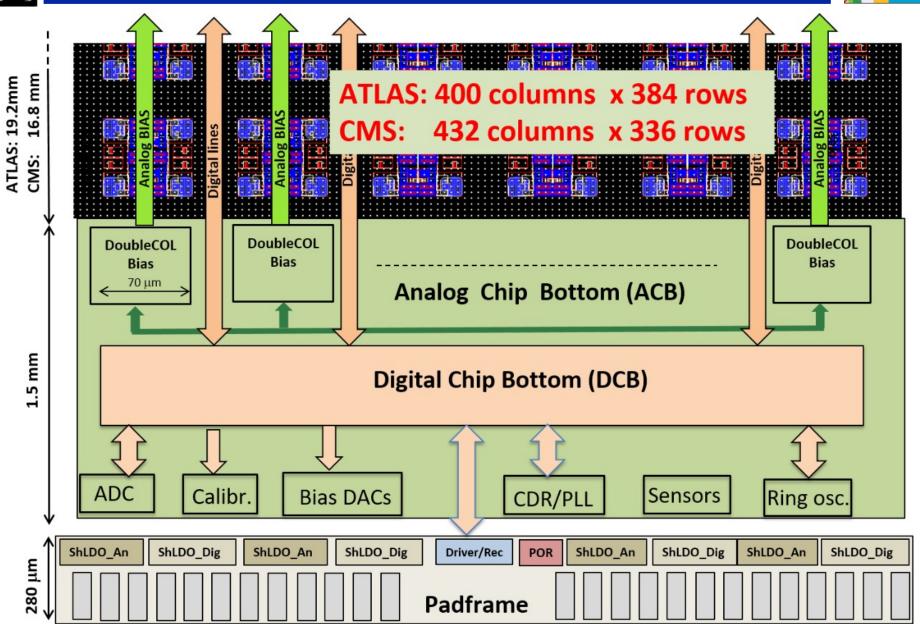

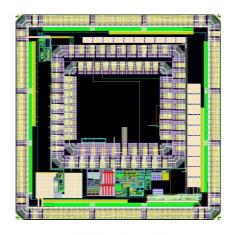

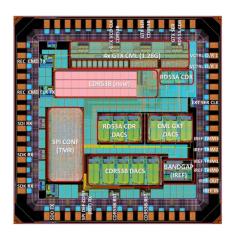

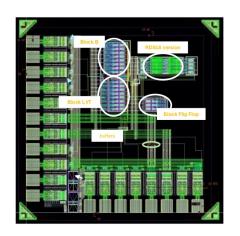

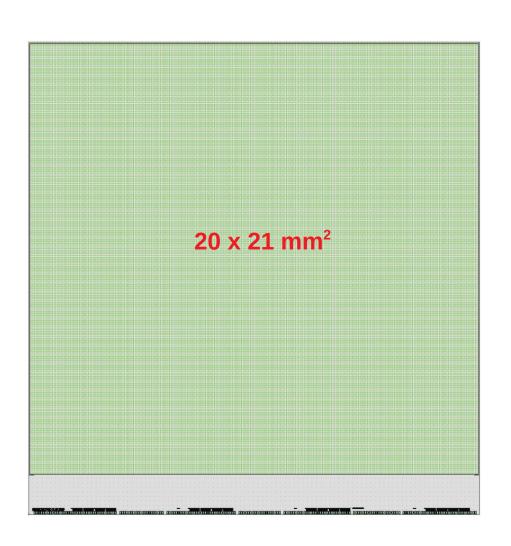

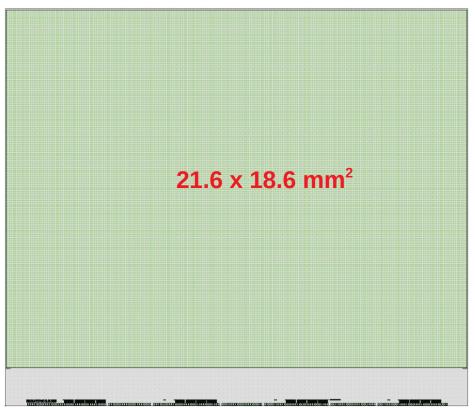

- Each chip is made of two RD53B elements: the chip bottom and a matrix of identical "cores". Each core has 64 pixels.

The main difference between ATLAS and CMS is the number of cores.

The analog front end Inside the core is also different.

The environment was designed to handle such variation.

### **One Core**

One flat synthesized circuit

~ 200k transistors

64 pixels in 16 "analog islands"

Whole core is stepped and repeated to make the pixel matrix

Hand-drawn transistors

"compiled software"

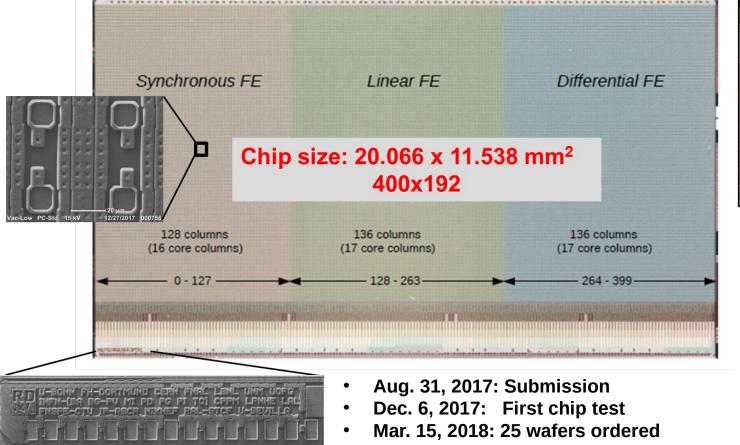

### RD53A

MPW together with CMS tracker chips

Apr. 13, 2018: First bump-bonded chip test

Chip doc on CDS: http://cds.cern.ch/record/2287593

### RD53B

# **RD53B Basic Specs**

| Technology                                | 65 nm CMOS                                      |

|-------------------------------------------|-------------------------------------------------|

| Pixel size                                | 50x50 um <sup>2</sup> & 25x100 um <sup>2</sup>  |

| Pixels (ATLAS/CMS)                        | 400 x 384 = 163,600 /                           |

|                                           | 432 x 336 = 145,152                             |

| Detector capacitance                      | < 100 fF (200 fF for edge pixels)               |

| Detector leakage worst case               | < 10n A (20 nA for edge pixels)                 |

| Detection threshold                       | <600 e-                                         |

| In-time threshold                         | <1200 e-                                        |

| Noise hits                                | < 10 <sup>-6</sup>                              |

| Hit rate                                  | < 3 GHz/cm <sup>2</sup> (75 kHz avg. per pixel) |

| Trigger                                   | 1 or 2-level configurable. Tag-based            |

| Max. 1-level readout rate                 | >4 MHz                                          |

| Max. 2-level readout rate                 | ~1 MHz                                          |

| 1-level max. latency                      | 12.5 us                                         |

| 2 <sup>nd</sup> level max. latency        | 25 us                                           |

| Hit loss at max hit rate                  | ≤ 1%                                            |

| Charge readout / resolution               | 4 bit readout / 6-bit to 4-bit @ 80 MHz         |

| Readout data rate                         | 1-4 links @ 1.28Gbits/s = max 5.12 Gbits/s      |

| Radiation tolerance                       | 500 Mrad at -15°C                               |

| SEU affecting whole chip                  | < 0.05 /hr/chip at 1.5GHz/cm² particle flux     |

| Power consumption at max hit/trigger rate | < 1 W/cm <sup>2</sup> including ShLDO losses    |

| Pixel analog/digital current              | 3-5uA/3uA                                       |

| Temperature range                         | -40°C ÷ 40°C                                    |

See requirements doc: https://cds.cern.ch/record/2663161 and manual: https://cds.cern.ch/record/2665301

8

### RD53B

# **New Feature Highlight**

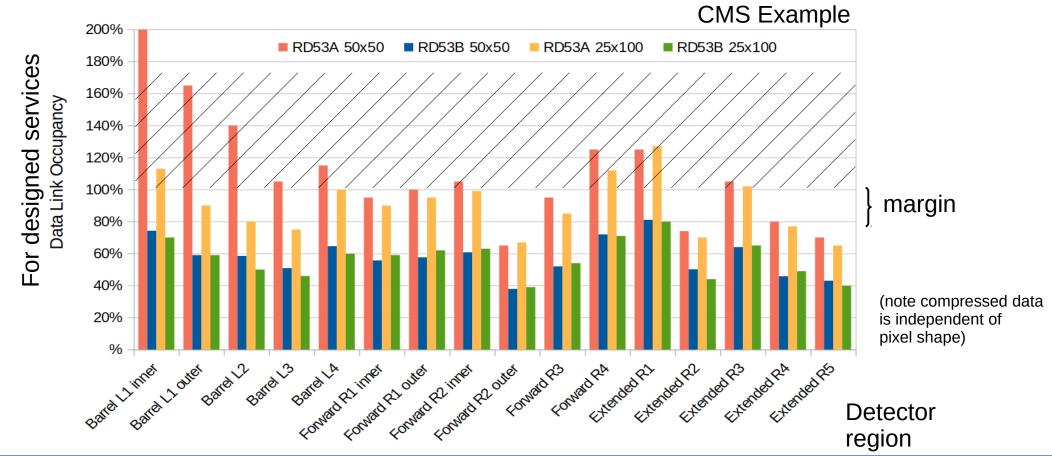

- Encoding with lossless compression used to send data off chip.

- Custom serial stream encoding to achieve compression AND be tolerant of corrupted fragments

- Important because, thanks to serial power, services volume (and mass) is dominated by data cables.

### **RD53B Status**

- All design work getting finishing touches this month

- Very significant amount of design work donenot just cut and paste from RD53A

- Almost every circuit has been touched at some level and several new functions (not in RD53A) have been added

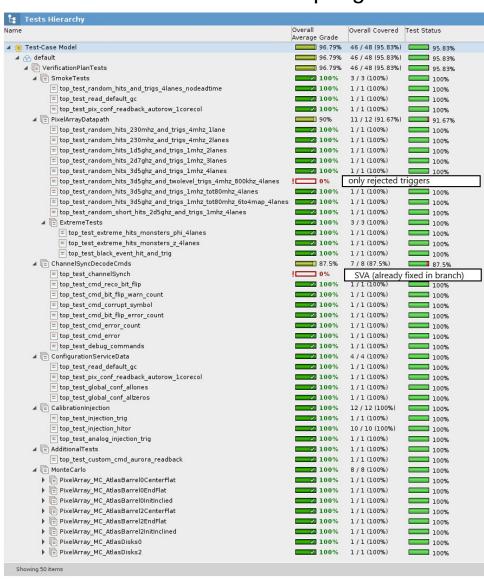

- Verification is critical. Advanced, but not yet completed

- Must reach a high level of confidence through verification in order to submit

- 143K lines of System Verilog code to verify 26.5K lines of chip code

- RD53 internal workshop in progress at CERN to check design and pour over all simulation and verification results

- ATLAS Final Design Review of ITkPix-V1 is on Friday

- Also must be completed before order for wafer run can be placed. https://indico.cern.ch/event/835605/

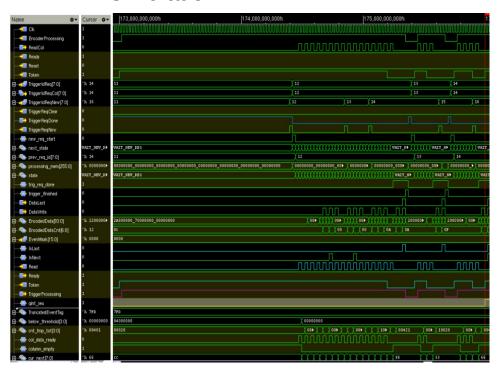

# **Verification / Simulation examples**

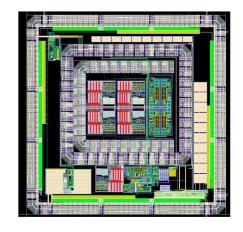

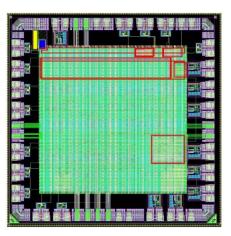

### RD53B Full chip digital

RD53B Full core Analog (with parasitics)

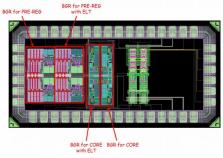

### **Circuits Validated in Silicon**

SLDO Testchip\_A

Submitted on August 2018

Bandgap Test Chip Submitted Aug. 2018

ADC Chip Submitted Aug. 2018

SLDO Testchip\_B

Submitted November 2018

CDR/PLL Test Chip Submitted Aug. 2018

SLDO Testchip\_C Submitted February 2019

Ring Oscillator Test Chip Submitted Nov. 2018

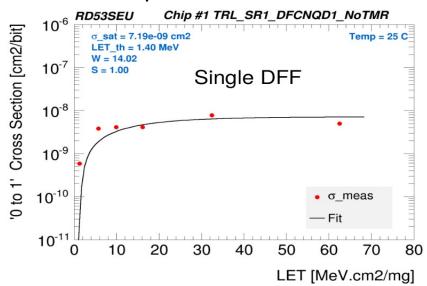

**SEU Test Chip** Submitted Aug. 2018

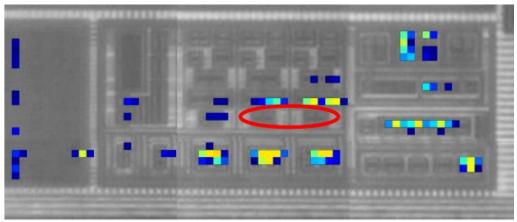

# **Single Event Effect Testing**

### Laser Injection on test chips

Whole VCO scanned in one run, focus closer to M1

### lons on test chips

# Charge injection in simulation

### **Conclusions**

- RD53 collaboration mandate has been extended to design the production pixel readout chips for ATLAS and CMS

- Configurable design called RD53B

- Will be instantiated first for ATLAS (submission this fall)

- ATLAS Final Design Review this Friday

- CMS chip submission will follow in 2020

- RD53B contains new features needed for production

- Extensive simulation and verification program significantly expanded relative to what was done for RD53A

- More info at cern.ch/RD53

# BACKUP

# **Design Team**

Collaboration board chair:

Lino Demaria, Torino

Interface to experiments: Co-spokespersons

Jorgen Christiansen, CERN (CMS), Maurice Garcia-Sciveres, LBNL (ATLAS)

· General organization, Funding, Specifications,

#### **Experiment observers**

**Duccio Abbaneo, CERN** (CMS), **Kevin Einsweiler, LBNL** (ATLAS)

#### RD53 design framework for final pixel chips: Flavio Loddo, Bari; Deputy: Tomasz Hemperek, Bonn

#### Floorplan/integration: Flavio Loddo, Bari

Pixel array, Bump pad, EOC, Power distribution, Bias distribution, Analog/digital isolation, Integration, Verification

#### Analog FEs with biasing: Luigi Gaioni, Bergamo;

Ennio Monteil, Torino; Amanda Krieger, LBNL

Specification/performance, Interface, Analog isolation, simulation model, Abstract, Integration, Verification

#### Monitoring:

Mohsine Menouni, CPPM; Gianluca Traversi, Bergamo, IP designers

Specification/performance, Interface, Analog isolation, simulation model, Abstract, Integration, Verification

#### PAD frame: Hans Krueger, Bonn

CDR/PLL: Piotr Rymaszewski, Bonn High speed drv: Konstantinos Moustakas, Tianyang Wang, Bonn Diff. IO: Gianluca Traversi, Bergamo

Plus many ATLAS/CMS groups not formally part of RD53

#### Digital integration:

Tomasz Hemperek, Bonn; Luca Pacher, Torino

Simulation Framework:

Sara Marconi, CERN;

Framework, Hit generation/import MC, Reference model / score board, Monitoring/verification tools, Readout rate estimations, Behavioural pixel chip, SEU injection.

#### · Pixel array logic:

Sara Marconi, CERN

- FE interface, Latency buffer, Core/column bus

#### Digital chip bottom:

Roberto Beccherle, Pisa; Francesco Crescioli, LPNHE;

- Configuration, Control interface, Readout data format/protocol, Compression

- Verification:

Sara Marconi, CERN; Attiq Rehman, Bergen,

Joel De Witt, Santa Cruz

Cesar Gonzales Renteria, LBNL

Peilian Liu, LBNL

SEU: Pedro Leitao, CERN; Rafael Girona, Sevilla

SET: Fernando Munoz Chavero, Sevilla

LPGBT: Pedro Leitao, CERN

Mixed signal: Luca Pacher, Torino;

Aikaterini Papadopoulou. LBNL

- Functional, SEU, Interfaces, specifications

#### Library cells:

DICE: Denis Fougeron, Mohsine Menouni, CPPM Timing characterization: Sandeep Miryala, FNL

#### **Serial Power:**

SLDO: Michael Karagounis, Andreas Stiller, Dortmund. Bandgap: Gianluca Traversi,

Verification: Alvaro Pradas, ITAINNOVA; Stella Orfanelli, CERN; Dominik Koukola, CERN

Shunt-LDO integration, On-chip power distribution, Optimization for serial powering, System level power aspects, Power Verification

#### Design for testability:

Giuseppe De Robertis, Bari

Scan path, BIST, production test patterns, Fault simulation, bump bonding testing

#### IPs: Support and possible updates

Current DAC: Bari Voltage DAC: Prague ADC, mux, temp: CPMM Power on reset: Seville Ring oscillator: LAL Analog buffer: RAL

#### Support and services:

Tools, design kit: Wojciech Bialas, CERN Repositories: Flavio Loddo, Bari; Luca Pacher, Torino; Tomasz Hemperek, Bonn Radiation model: Mohsine Menouni, CPPM; CERN

#### Testing: Timon Heim, LBNL

YARR system: Timon Heim, LBNL BDAQ53 system: Marco Vogt, Michael Daas, Yannik Dieter, Hans Krueger, Tomasz Hemperek, Mark Standtke Bonn Radiation test: Luis Miguel Jara Casas, CERN, Mohsine Menouni, CPPM.

Names in bold: Member of RD53 management board

#### Pixel sensor and bump-bonding:

Fabian Huegging, Bonn (ATLAS), Georg Steinbrueck, Hamburg (CMS)

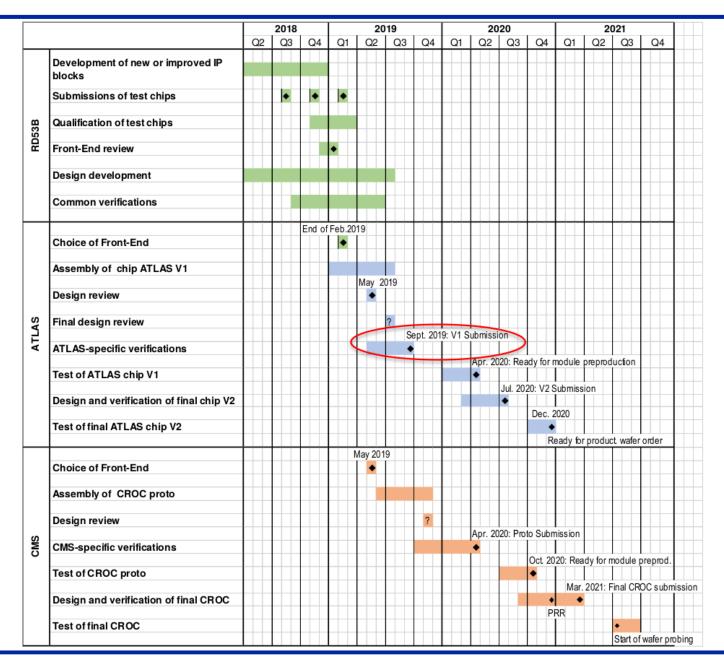

### **Schedule**

### **RD53B New Features**

- Selected Diff. Front End for ATLAS, Lin. FE for CMS

- Added edge, top, and corner pixel biases

- Upgraded calibration injection & corrected column variation

- New hit synchronization and ToT with 6b-to-4b compression

- Redesign of the startup and generation of reference voltages

- Improvement of SLDO and addition of low power mode

- Addition of overcurrent and overvoltage protection

- Redesigned PLL for lower jitter and robust locking

- Added trigger tags and new readout format with compression

- Added 2-lever trigger for ATLAS and self-trigger

- Added suppression of low charge isolated hit backgrounds

- Added data aggregation between chips

- Changed reset scheme to synchronous and added CMD activity reset

- Extensive triplication and SEU hardening

- Added new resistive temperature sensors and E-fuses for SN

- Added precision ToT and ToA

- Enlarged wire bond pads

# RD53B-ATLAS & CMS side-by-side

### **RD53A Database**

Database of RD53A chips in use at cern.ch/rd53a-chips

**Current Wafer: 3**

|               |               |               |                  | 05-01<br>MISSING    | 06-01<br>MISSING    |               |               |                   |               |

|---------------|---------------|---------------|------------------|---------------------|---------------------|---------------|---------------|-------------------|---------------|

|               |               |               | 04-02<br>CERN    | 05-02<br>CERN       | 06-02<br>DEMOKRITOS | 07-02<br>CERN | 08-02<br>CERN |                   |               |

|               | 02-03<br>CERN | 03-03<br>RBI  | 04-03<br>CERN    | 05-03<br>CERN       | 06-03<br>LBNL       | 07-03<br>LBNL | 08-03<br>CERN | 09-03<br>CERN     |               |

|               | 02-04<br>CERN | 03-04<br>CERN | 04-04<br>CERN    | 05-04<br>CERN       | 06-04<br>LBNL       | 07-04<br>ETH  | 08-04<br>CERN | 09-04<br>COLORADO |               |

|               | 02-05<br>CERN | 03-05<br>CERN | 04-05<br>CERN    | 05-05<br>CERN       | 06-05<br>CERN       | 07-05<br>ETH  | 08-05<br>UNM  | 09-05<br>COLORADO | 10-05<br>ETH  |

| 01-06<br>CERN | 02-06<br>CERN | 03-06<br>CERN | 04-06<br>CERN    | 05-06<br>CERN       | 06-06<br>CERN       | 07-06<br>ETH  | 08-06<br>ETH  | 09-06<br>COLORADO | 10-06<br>ETH  |

| 01-07<br>CERN | 02-07<br>ETH  | 03-07<br>CERN | 04-07<br>CERN    | 05-07<br>CERN       | 06-07<br>CERN       | 07-07<br>ETH  | 08-07<br>CERN | 09-07<br>COLORADO | 10-07<br>ETH  |

| 01-08<br>CERN | 02-08<br>CERN | 03-08<br>CERN | 04-08<br>FIRENZE | 05-08<br>DEMOKRITOS | 06-08<br>CERN       | 07-08<br>ETH  | 08-08<br>CERN | 09-08<br>PURDUE   | 10-08<br>ETH  |

|               | 02-09<br>CERN | 03-09<br>CERN | 04-09<br>CERN    | 05-09<br>CERN       | 06-09<br>CERN       | 07-09<br>CERN | 08-09<br>CERN | 09-09<br>PURDUE   | 10-09<br>CERN |

|               | 02-10<br>CERN | 03-10<br>CERN | 04-10<br>CERN    | 05-10<br>DEMOKRITOS | 06-10<br>ETH        | 07-10<br>CERN | 08-10<br>CERN | 09-10<br>ETH      |               |

| '             |               | 03-11<br>RBI  | 04-11<br>CERN    | 05-11<br>CERN       | 06-11<br>CERN       | 07-11<br>CERN | 08-11<br>CERN |                   |               |

|               | '             |               | 04-12            | 05-12               | 06-12               | 07-12         |               |                   |               |

CERN

| Serial Number    | 0x0385                                                        |

|------------------|---------------------------------------------------------------|

| Diced Location   | IZM                                                           |

| Diced Date       | 2018-08-01 12:00:00                                           |

| Thickness        | 350 nm                                                        |

| Bumped           | False                                                         |

| Sensor           | NONE                                                          |

| Flip Date        | 2019-04-30 12:00:00                                           |

| Board            | 365                                                           |

| Board Date       | 2018-11-14 12:00:00                                           |

| Status History   | 2019-04-30 - All Good<br>2018-11-14 - Untested                |

| Location History | 2019-04-30 - UNM<br>2018-11-14 - FIRENZE<br>2018-08-27 - CERN |

| Radiation (Mrad) | None                                                          |

| Chip Comment     |                                                               |

| Board Comment    | In SCC card                                                   |

| Board Type       | 1: Bonn SCC                                                   |

CERN

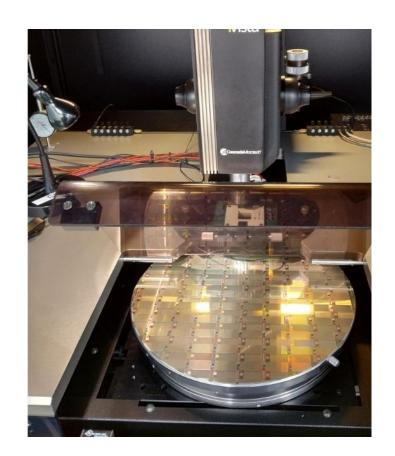

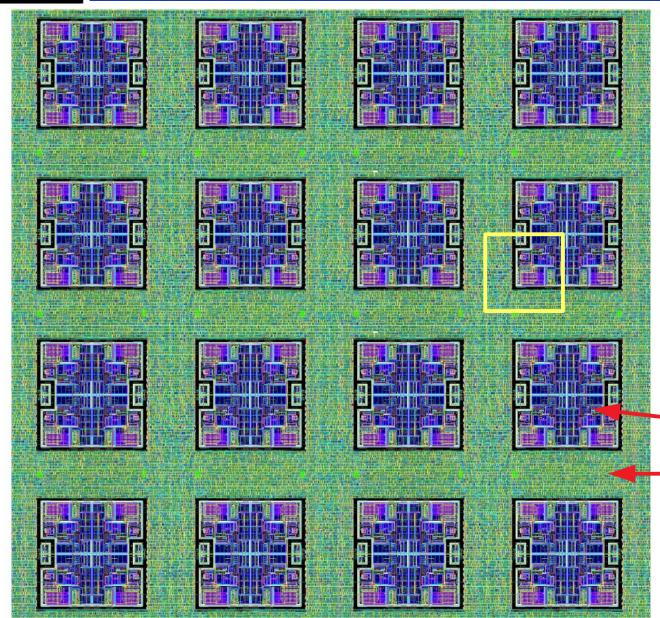

## **RD53A Wafer Probing**

### Wafer Probing

- Probed 58 wafers in total

- 41 in Bonn (for RD53 and ATLAS)

- 17 at CERN (for CMS)

- 89 chips per wafer: Over 5000 chips for statistical analysis

- Designated in parts for RD53, ATLAS and CMS

- Test procedure very stable

- Results look as expected